激情洋溢的平台转型之路 – Xilinx数据中心专家解读XDF

demi 在 周四, 12/12/2019 - 09:37 提交

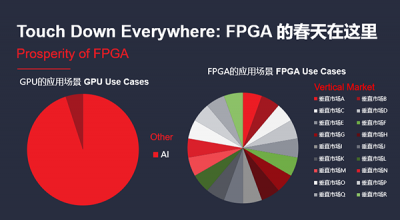

赛灵思大中华区数据中心专家级工程师王晓群:面对异构计算的潮流,赛灵思正毫不犹豫地将骨子里的创新与激情释放出来。这种毫无保留源自于公司对于趋势和技术的精准把握,和对业界开发者的信心。

赛灵思大中华区数据中心专家级工程师王晓群:面对异构计算的潮流,赛灵思正毫不犹豫地将骨子里的创新与激情释放出来。这种毫无保留源自于公司对于趋势和技术的精准把握,和对业界开发者的信心。

什么是时序约束?泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。因此如果我们不加时序约束,软件是无法得知我们的时钟周期是多少,PAR后的结果是不会提示时序警告的。

2019 赛灵思开发者大会( XDF )亚洲站于北京胜利闭幕。赛灵思总裁兼 CEO Victor Peng 发表了“赛灵思:创新驱动力”为题的主题演讲,分享了公司启动三大战略一年多来所取得的重大成就。

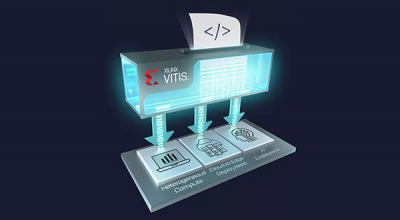

还在为错过XDF上Lab Zone的案例体验而锤头顿足吗?还在为不知道如何部署和使用Vitis与Vitis AI而心灰意冷吗?大家都可以通过以下Vitis Acceleration Lab中精选出来的优秀技术分享案例来学习与跟进,帮助大家指导和使用Vitis。

12 月 8 日,第三届全国大学生 FPGA 创新设计竞赛颁奖典礼在南京市江北新区成功举办。来自江南大学的江南B318团队、来自东南大学的 “CCCTV10” 团队和“串串最好吃”团队获得赛灵思企业特别奖。赛灵思作为协办单位之一,第三次全程参与这项全国性大学生 FPGA 竞赛,继续为竞赛提供从产品到技术培训的全面支持。

描述使用UltraScale™和UltraScale +™器件进行PCB和接口级设计的策略。

RGB 图像转灰度图像的计算,即由当前像素点的 RGB 值计算 YUV 色域的 Y 通道的数值

“要养成良好的Verilog代码风格,要先有硬件电路框图之后再写代码的习惯,设计出良好的时序,这样才能在FPGA开发或者ASIC设计中起到事半功倍的效果,否则会事倍功半。”

本文想针对测试中一种很常见的测试场景,即参数化测试,继续聊聊关于测试的话题,并尝试将这几个测试框架串联起来,做一个横向的比对,加深理解。

在进行加减乘除运算时一定要注意位宽,保证足够大的位宽,防止数据溢出,如果溢出结果就会出现错误,尤其是加和乘运算,一定要计算好位宽(位宽的计算可以都取其最大值,看最大值计算后的位宽就是最大位宽,采用这个位宽数据就溢出不了)。