关于P4编程语言的几个误区

judy 在 周四, 06/20/2019 - 09:32 提交

近几年SDN之父Nick教授身体力行的开始改造OpenFlow,网络设备第一次和计算设备一样具有了可编程的能力。和OpenFlow刚刚面世一样,用于网络设备编程的P4编程语言也存在众多误解。本文的主要目的就是解惑P4编程语言的几个常见误区。

近几年SDN之父Nick教授身体力行的开始改造OpenFlow,网络设备第一次和计算设备一样具有了可编程的能力。和OpenFlow刚刚面世一样,用于网络设备编程的P4编程语言也存在众多误解。本文的主要目的就是解惑P4编程语言的几个常见误区。

本篇咱们来聊一聊高级的IO逻辑资源。所谓ISERDESE2模块,即Input serial-to-parallel converters。该模块的作用就是实现高速源同步输入数据的串并转换。所谓OSERDESE2模块,即output parallel-to-serial converters。该模块的作用就是实现高速源同步输出数据的并串转换。

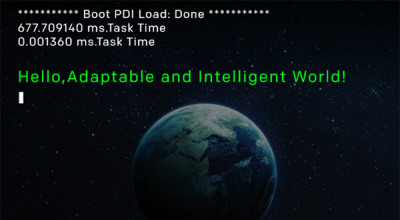

首先这将是一个由一系列视频所组成的连续剧,我们从看着第一颗芯片在台积电诞生,看着它坐上飞机,远渡重洋来到了硅谷,我们又跟着它的视角进入到了赛灵思的实验室......所有的工程师团队都围绕在它的身边,注视着它,直到它向世界说出它的第一句问候......

ACAP 是一种高度集成的多核异构计算平台,可在软硬件两个层面随时进行更改,从而动态地适应数据中心、汽车、5G 无线、有线以及国防市场的广泛应用与工作负载需求。

自适应和智能计算的全球领先企业赛灵思公司今天宣布已开始面向参与公司“早期试用计划”的多家一线客户交付 Versal™ AI Core 和 Versal™ Prime 系列器件。Versal 是业界首款自适应计算加速平台(ACAP),这是一款具有革命性意义的新型异构计算器件,其功能远超传统的 CPU、GPU 和 FPGA。

作者:hankf,Xilinx Employee

Ubuntun 16.04系统,PetaLinux 2019.1 执行"petalinux-config", 失败。

本篇主要以Xilinx的xc7z010 的SOPC(zybo的开发板)为硬件平台,在以下几方面介绍:以zynq 7000的逻辑资源(PL)搭建CRTC/Encoder/Connector硬件模块,以HDMI输出接口为例,介绍各个模块的接口特性;会先给出DRM+KMS驱动框架下的主要模块,并针对上述硬件子模块分析对应的内核驱动部分;

CTAccel 图像处理 (CIP) 加速器是一款基于 FPGA 的图像处理加速解决方案,可通过将计算负载从 CPU 转移至 FPGA,显著提高图像处理及图像分析的性能。CIP 强大的处理能力可为数据中心带来极大的优势,可将图像处理吞吐量提高 3-7 倍,将计算时延缩短 3 倍,并可将总体拥有成本降低 3 倍。

双口RAM的读写冲突问题在FPGA调试中经常遇到......在初学FPGA调试中,常常为了所谓的省事,在写代码设计仿真阶段就忽略了双口RAM的读写冲突问题,导致在FPGA上板调试中浪费大量的时间。本文就针对以往出现的双口RAM读写冲突问题展开讨论,希望能够给大家提个醒。

Skreens 是一款个性化的流媒体视频引擎,可为广播、企业协作、游戏、安全和数字媒体等产业实现创新的视觉体验。