PCIx系列之“M-PCIe”

demi 在 周三, 09/25/2019 - 13:40 提交

M-PCIe即Mobile PCIe,主要应用对象是智能手机等嵌入式设备。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于标准的PCIe总线,M-PCIe ECN主要的改动在物理层,通过引入M-PHY,旨在获得更低的功耗以适应嵌入式设备的低功耗要求。

M-PCIe即Mobile PCIe,主要应用对象是智能手机等嵌入式设备。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于标准的PCIe总线,M-PCIe ECN主要的改动在物理层,通过引入M-PHY,旨在获得更低的功耗以适应嵌入式设备的低功耗要求。

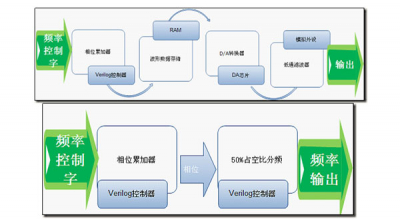

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。首先讲述DSS(直接频率合成法)的原理。DDS是重要的频率合成方法,在波形发生器中有极其重要的应用。DDS主要由几部分组成:a) 相位累加器;b) RAM数据读取;c) D/A转换器;d) 低通滤波器。

根据维基百科定义:字符串是由零个或多个字符组成的有限序列。而在Python 3中,它有着更明确的意思:字符串是由Unicode码点组成的不可变序列(Strings are immutable sequences of Unicode code points.)

我们知道xilinx FPGA的selectio中有ilogic和ologic资源,可以实现iddr/oddr,idelay和odelay等功能。刚入门时可能对xilinx的原语不太熟练,在vivado的tools-> language templates中搜索iddr idelay等关键词,可以看到A7等器件下原语模板。复制出来照葫芦画瓢,再仿真一下基本就能学会怎么用了。

Spartan6系列FPGA常见的配置模式有5种,由模式输入管脚M1、M0决定。该5种模式可分为3大类,1. JTAG模式(可归为从模式);2. 主模式;3. 从模式。

在ZYNQ进阶之路3中我们讲解了PL端UART 发送的设计,本节我们讲解PL端实现串口UART的接收设计。

通过异构多处理、I / O 灵活性、基于硬件的确定性控制以及在网络安全、安全性和机器学习领域的全面解决方案,满足可扩展医疗保健平台不断增长的需求。

发起沿和捕获沿(Launch edge & Capture edge)

上一篇咱们介绍了7系列FPGA的整体时钟架构,知道了FPGA是由很多个时钟区域组成,时钟区域之间可以通过Clock Backbone 和CMT Backbone来统一工作。本篇咱们就说一下时钟区域的内部结构。

9月20日,米尔携手电子发烧友、电路城、面包板三大平台举办的MYD-C7Z010/20开发板试用活动正式上线啦!本次试用活动,是米尔回馈给各位电子工程师的重磅福利,只要您积极配合参与活动, 价值1450元 的MYD-C7Z010/20开发板试将免费赠送。