【视频】Vitis™ 统一软件平台简介 (中文字幕)

demi 在 周四, 10/10/2019 - 09:59 提交

Vitis 独立于 Vivado™ 设计套件,后者仍然继续为希望使用硬件代码进行编程的用户提供支持。但是,Vitis 也能够通过将硬件模块封装成软件可调用的函数,从而提高硬件开发者的工作效率。

Vitis 独立于 Vivado™ 设计套件,后者仍然继续为希望使用硬件代码进行编程的用户提供支持。但是,Vitis 也能够通过将硬件模块封装成软件可调用的函数,从而提高硬件开发者的工作效率。

10月9日,赛灵思大中华区销售副总裁唐晓蕾 ( Maria) 及赛灵思软件和人工智能高级经理罗霖( Andy )在北京隆重发布里程碑式的 Vitis™ 统一软件平台,以“突破软硬壁垒,解锁全员创新” 为主题,揭开赛灵思通过软件革新,解锁软件开发者的硬件加速壁垒,将赛灵思独特的自适应计算能力带给全员开发者的新篇章。

由于本人习惯在Windows环境下做FPGA开发,因此将PetaLinux安装在Linux虚拟机中,开发环境如下:Windows 10;Vivado 2018.2.1;VMware Workstation 14 Pro;Ubuntu 16.04.5 desktop amd64;Petalinux 2018.2。

首先来理清楚MIO与EMIO的关系。MIO是PS的I/O引脚,一共有54个,分为Bank0与Bank1,可以接许多外设比如UART、SPI或GPIO等,另外可以引脚复用。

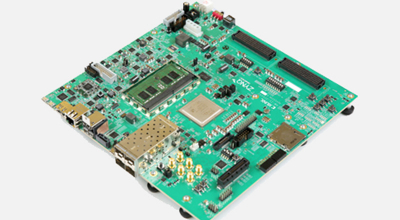

FPGA是可编程芯片,因此FPGA的设计方法包括硬件设计和软件设计两部分。硬件包括FPGA芯片电路、 存储器、输入输出接口电路以及其他设备,软件即是相应的HDL程序以及最新才流行的嵌入式C程序。

如果将计算机比作人的话,CPU就是人的大脑,而PCIe就是人的神经中枢,负责内部数据信息的传输。

Zynq中的UART支持轮询和中断驱动两种模式。本文给出使用中断驱动模式的例子,完成与26篇中轮询模式下相同的功能,即UART收到8字节数据后执行某项操作。对比之下,体会中断驱动模式的特点。

Xilinx Zynq®-7000全可编程SoC提供了一个灵活的平台,在启动新解决方案的同时,为传统ASIC和SoC用户提供完全可编程替代方案。下面,就让我们来了解一下这款产品吧。

PetaLinux 是一种嵌入式 Linux 软件开发套件 (SDK),主要用于赛灵思 FPGA 基片上系统设计。本指南可帮助读者熟悉实现 PetaLinux 全面用途的工具。

PCI,英文全称:PeripheralComponent Interconnect,外围组件互联,由Intel于1991年提出。随着Intel Pentium处理器诞生而迅速发展,当时几乎所有的外围设备,从硬盘控制器、声卡、显卡和网卡,都使用PCI插槽来连接到计算机的主板上。