【视频】Xilinx:加速视频及图像处理

demi 在 周二, 09/17/2019 - 09:28 提交

赛灵思视频加速技术研讨会上,讲师”Sean Gardner"作演讲“加速视频及图像处理”。

赛灵思视频加速技术研讨会上,讲师”Sean Gardner"作演讲“加速视频及图像处理”。

在 ZYNQ进阶之路1 中我们讲解了PL端LED流水灯的工程的建立,编码,综合和下载!本节主题,PL端PWM输出设计,讲解怎么用ZYNQ PL端简单实现2通道PWM波输出,其中工程创建过程以及综合生成bit文件过程不再累述!

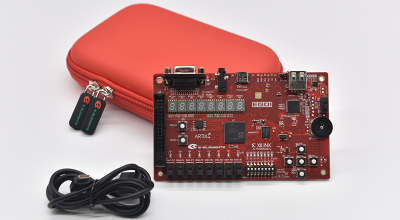

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

忘了在哪看到一位编程大牛调侃,他说程序员每天就做两件事,其中之一就是处理字符串。相信不少同学会有同感。几乎任何一种编程语言,都把字符串列为最基础和不可或缺的数据类型。而拼接字符串是必备的一种技能。今天,我跟大家一起来学习Python拼接字符串的七种方式。

接上文:Xilinx AI 方案与资源更新一览(一) 全新成功案例——百度将赛灵思 ZU5 用于 Apollo ACU Advanced,百度在 2019 年 7 月于北京举办的年度 AI 开发者大会上推出用于自动代客泊车 (AVP) 的 Apollo ACU Advanced。

赛灵思视频加速技术研讨会上,讲师”廖玉峰"作演讲“高效视频处理与 AI 融合架构”。

本文简单介绍Zynq中的UART控制器,重点放在编程所需了解的知识。很多功能使用库函数可以快速配置,因此没必要仔细了解每个寄存器是干什么的这种问题,应把精力放在UART的特性、工作原理和可实现功能方面。

在设计仿真激励文件时,为了满足和外部芯片接口的时序要求,经常会用到延时赋值语句,由于不同的延时赋值语句在仿真过程中行为不同,会产生不同的激励输出,如果不认真区分不同表达式引起的差异,就可能产生错误的激励,无法保证仿真结果的正确,本文就是区分各种延时赋值语句的差异,并给出比较结果。

时间:2019年9月26日上午10:00 - 11:30,本次研讨会同时适用于 边缘(Edge)和云(Cloud)应用,内容将包含:AI 技术与应用的趋势和挑战;赛灵思 AI 应用和技术的最新进展;与 AI 从业人员的互动探讨。

第二代 Zynq UltraScale+ RFSoC 器件现已量产!!屡获殊荣的赛灵思 Zynq® UltraScale+™ RFSoC,将高性能数据转换器集成于一个硬件可编程的 SoC 上,是面向 5G 海量 MIMO 的业界唯一自适应单芯片射频平台。第二代器件现已全面量产,可立即支持最新 5G 应用。