Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟篇

demi 在 周四, 11/21/2019 - 11:55 提交

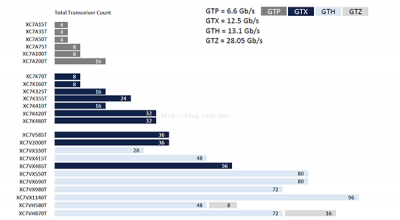

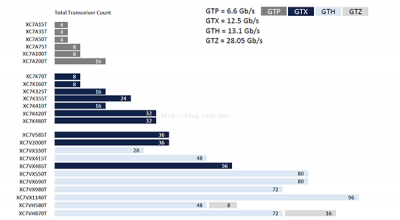

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同。

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同。

Xilinx 与 NTU 联手举办首届女子 Hackathan 2019

嵌入式人工智能自动驾驶领导者魔视智能宣布,将携其基于赛灵思汽车级异构计算平台 Zynq® UltraScale+™ MPSoC 的全新自适应前装量产自动泊车系统亮相赛灵思开发者大会 (XDF)。

XTP系统拥有“极速交易、极速行情、极致风控、极致体验”等核心性能及优势,赛灵思是自适应计算技术与方案的领导企业。在本届开发者大会上,中泰证券将与赛灵思公司强强联手,带您体验 FPGA 为 Fintech 应用所带来的极速体验。

忠告一:如果时序差的不多,在1NS以内,可以通过修改综合,布局布线选项来搞定,如果差的多,就得动代码。

Non-posted(非转发)事务和-posted(转发)事务都是PCIE TLP(事务层包)类型。Non-posted TLP有返回TLP,而posted事务没有返回。记忆技巧:非转发事务非要返回。本文中说的事务指的是PCIE事务层TLP。

在实现多级CIC滤波器前我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理。CIC滤波器在通信信号处理中有着重要的应用。

宇宙的起源是什么?什么是物质和能量?为了回答这个世界上最具挑战性,也是最终极,最玄妙的科学问题,欧洲核子研究组织成立了欧洲粒子物理实验室 (CERN),这是一个由 20,000 名科学家组成的联盟,旨在探索宇宙的起源。但为了做到这一点,研究人员必须突破技术的限制。

当今时代,服务提供商推出的依赖于 AI 与即时响应功能的实时服务层出不穷,这些服务都非常适合 FPGA 加速,而这,也正是赛灵思之所以在2018年推出 Alveo 数据中心加速器卡的重要推动因素之一。Alveo 加速器卡的设计,致力于大幅提升云端和本地数据中心中行业标准服务器的性能。

滤波是一个邻域操作算子。通常,邻域选择3x3,5x5等,这些3x3或者5x5的邻域,被称作滤波器,掩模或核。利用给定像素邻域内的像素值与掩模做卷积,从而决定该像素的最终输出值。