ZYNQ开发(五)双核启动

judy 在 周二, 06/04/2019 - 11:07 提交

ZYNQ是一种主从关系的AMP架构,通过松散耦合共享资源,允许两个处理器同时运行自己的操作系统或者裸机应用程序,在各自运行自己的程序或者系统的时候,可以通过共享内存进行双核之间的交互。双核启动中,cpu0完成系统的初始化,与cpu1进行通信,读写共享内存

ZYNQ是一种主从关系的AMP架构,通过松散耦合共享资源,允许两个处理器同时运行自己的操作系统或者裸机应用程序,在各自运行自己的程序或者系统的时候,可以通过共享内存进行双核之间的交互。双核启动中,cpu0完成系统的初始化,与cpu1进行通信,读写共享内存

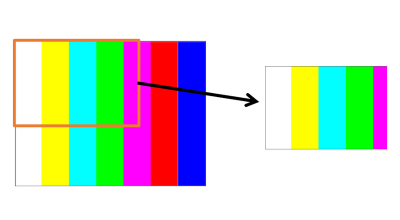

上篇咱们简单的说了I/O的电气特性,本篇咱们接着介绍I/O逻辑资源,先贴上两张图。图1为HPBANK的I/O模块,图2为HRBANK的I/O模块,两者区别在于后者无ODELAYE模块。

使用 Xilinx SoC 和 FPGA 从单轴控制扩展到多轴控制,可带来嵌入式分析及毋庸置疑的确定性、高性能和高功率效率。

ZCU104 评估套件可帮助设计人员为监控、高级驾驶员辅助系统 (ADAS)、机器视觉、增强实境 (AR)、无人机和医学成像等嵌入式视觉应用快速启动设计。该套件采用带视频编解码器的 Zynq® UltraScale+™ MPSoC EV 器件,支持嵌入式视觉使用案例的许多常见外设及接口。

米尔近期隆重推出首款Zynq UltraScale+ MPSoC平台核心板(及开发板):MYC-CZU3EG。其搭载的XILINX新一代Zynq处理器(具体型号XCZU3EG-1SFVC784,未来可选用XCZU2CG,XCZU3CG.XCZU4EV,XCZU5EV), 采用16纳米制程,相比Znyq7000系列每瓦性能提升5倍

本文会尽量从初学者的角度去描述整个Linux整个图形子系统,但由于其复杂性,涉及到的模块比较多,可能会需要一些相关的先验知识;对于系统的介绍,分析的着重点可能不会在于为什么该这样设计,而是在于在现有的显示系统下,我们能做些什么来适配我们的目的;

每个Cortex-A9处理器都有私有的32位定时器和32位看门狗定时器。这两种定时器都是32位的计数器,计数到0时产生中断;带有8位的预分频器,能够更好地控制中断周期;可配置为单次重载或自动重载模式;可配置初始值。它们的工作时钟固定为CPU频率的1/2(CPU_3x2x)

VCU128 开发板采用全新 Xilinx VU37P HBM FPGA,利用堆叠芯片互连将 HBM 裸片添加到封装基板上的 FPGA 裸片旁边。支持高带宽存储器(HBM) 的 Xilinx FPGA 是计算带宽问题(与在 PCB 上使用 DDR4 等并行内存相关)的明确解决方案。

该视频系列 26 展示的是可以如何使用 AXI Video Direct Memory Access (VDMA) IP 来实现视频剪裁、画中画或软模式生成器功能。

从普通消费电子到工业智能应用,从FPGA到全可编程器件的发展,这是FPGA技术在持续发力拓展多方市场,也在持续适应更多的未来需求的转型步伐。赛灵思作为一家FPGA芯片制造商,在工业物联网(IIoT)和医疗物联网(HcIoT)这些新领域中,有怎样的表现?