一大波 AI/ML 工具与素材更新!

judy 在 周三, 07/10/2019 - 09:33 提交

ML Suite V1.4 更新

赛灵思机器学习套件(ML Suite) v1.4 已于 5 月 24 日发布,主要更新功能包括:

ML Suite V1.4 更新

赛灵思机器学习套件(ML Suite) v1.4 已于 5 月 24 日发布,主要更新功能包括:

基于赛灵思技术的系统可以结合人工智能,通过采用“可预测性维护”的方案减少设备停机时间,从而最大限度地提高生产力。赛灵思的基于 Python 和神经网络的Edge AI 解决方案简化了硬件加速的可预测维护方案的实现,从而可以持续性地监控重要资产,分析数据,以及智能地为这些系统规划服务。

本视频重点介绍了 Vivado 设计套件 2019.1 版本中的新增功能,包括对操作系统以及器件的支持情况,还有高层次增强功能,以及各种功能改进以加速设计集成、实现和验证的过程

为新无线标准制定和部署验证或生产测试策略是十分困难的。而随着5G NR等新无线标准和技术的复杂性不断增加,这方面工作的难度进一步加大。其中的挑战包括更宽且更复杂的波形、测试点数量呈指数级增长,以及使用波束成形和相控阵天线等技术来改善有限的链路预算

Accelize 可为 FPGA 加速应用和 IP 核提供 DRM 支持的分配平台,通过即时、可扩展的安全部署为全球客户提高收入。 该平台支持任何 CSP,如AWS、华为、阿里巴巴、Nimbix 或 Xilinx Alveo 板卡,用于本地部署

XAPP1026中记录一些lwIP的应用程序示例和性能测试情况,不过提供的示例工程都是在几个Xilinx的官方板子中跑的。可能很多学生没有机会碰到这些板子。。。另外这份应用笔记使用的SDK 2014.3版本也比较老,那个版本lwip还没有直接集成到SDK中。本文将这份笔记其中比较有用的代码编写思路和性能测试结果部分摘取出来

上个月,兰斯大学(University of Reims)成功举办了一场研讨会,就OpenPOWER基金会、POWER9和PowerAI进行探讨交流。该大学的教师、学生与来自IBM POWER Systems、 EBV Elektronik以及巴塞罗那超算中心的专家们济济一堂,分享知识、交流技术、碰撞智慧,呈现了一场精彩的思想盛宴!

了解Xilinx嵌入式软件栈和工具在2019.1版本中的新功能和更新。

本入门文章由两部分组成,旨在介绍JESD204C标准,着重说明其与JESD204B的不同之处,并详细阐明为达成上述目标、提供对用户更友好的接口、实现各行各业的带宽能力需求而引入的关键新特性。本系列的第一部分概述版本差异和新特性,第二部分将深入探讨最重要的新特性

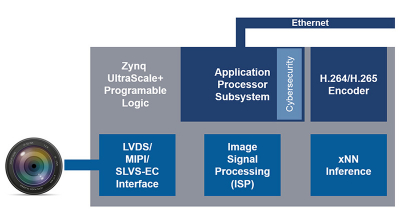

随着自定义图像信号处理 (ISP) 技术的出现,基于神经网络的机器学习推断正迅速成为监控设备制造商实现差异化所依靠的主要方法。Xilinx 通过以下方式提供高效、可扩展的定制化