2019 SEU-Xilinx暑期学校扬帆起航

judy 在 周一, 07/08/2019 - 09:08 提交

昨天,2019年SEU-Xilinx国际暑期学校正式在南京集成电路产业服务中心扬帆起航,100多位学员在炎炎烈日中投身于暑期学习,希望他们接下来12天的付出都能够取得成果。

昨天,2019年SEU-Xilinx国际暑期学校正式在南京集成电路产业服务中心扬帆起航,100多位学员在炎炎烈日中投身于暑期学习,希望他们接下来12天的付出都能够取得成果。

一般情况下,我们会专门下载第三方交叉编译工具链进行Xilinx器件的Linux开发(工具链获取:git clone https://github.com/xupsh/Codesourcery.git)。但是,Xilinx在其SDK下集成了交叉编译工具链

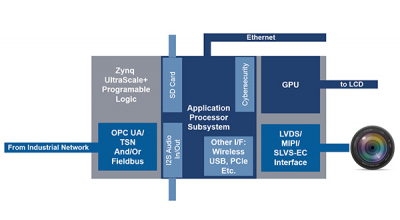

集成性、智能性以及最高功耗性能比可实现功能强大的小型视觉解决方案

由于高带宽接口和低时延像素级处理,Xilinx FPGA 广泛应用于机器视觉传感器接口和采集卡。随着智能相机及其它形式的嵌入式视觉智能应用的兴起,Xilinx SoC 现已成了小型高性能视觉应用的最佳解决方案,因为其单片集成:

赛灵思无线系统架构师Matt Ruan应MWC上海组委会邀请,在5G网络论坛上做了该演讲,演讲中 Matt 向大家详细介绍了赛灵思在5G 推广中所担负的角色和定位,以及在整个 5G 产业链路中赛灵思产品所覆盖的几乎所有节点。演讲中Matt还介绍了赛灵思最新出货的业界首款 Versal ACAP的主要特性,以及它将在未来通信领域所能担负的关键作用。

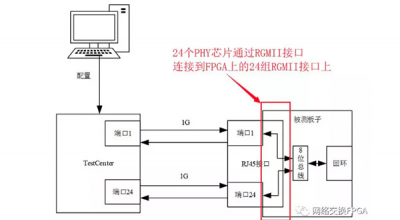

实验室回来一批板子,上面有RGMII接口、SGMII接口等各种接口,怎么测试这些网口是否正常呢?的确需要一些经验。比如RGMII接口,最重要的是看在哪里去做的时钟和数据偏移。这时,常常需要使用VIO去读取PHY里面对应寄存器的值,看是否工作在正常RGMII接口时序模式。

前几篇咱们说了FPGA内部逻辑,本篇咱们再聊一聊7系列FPGA的供电部分

此博客面向想要开始使用 PetaLinux、了解其关键工具、概念和功能的任何人。在第一篇博客文章中,我们将介绍如何针对 ZCU102 开发板创建 PetaLinux 工程,以及如何修改镜像

HMI 可作为用户来往信息的枢纽,无论用户设备是在工厂车间、是远程 SCADA 系统、手持设备和可穿戴设备的一部分,还是整合在运营商控制的任意数量或类型的资产中,都不例外。现代 HMI 提供融合本地数据和云数据的容量,从而可提供对流程或任务清晰的洞察,但随着端点计算的兴起

本视频演示了 Versal™ ACAP 的 32 Gb/s 串行收发器,以及目前同类最佳的 UltraScale+ GTY 收发器改进后的形态。

根据美国土木工程师学会(ASCE)发布的2017年基础设施报告卡,美国614,387座桥梁中近40%至少有半个世纪的历史。2016年,近10%的车辆在结构上存在缺陷。平均每天有1.88亿辆车跨越结构上不足的桥梁。桥梁的管理者们不断寻找更能减小成本效益的方法来保持桥梁的良好维修