紫光同创荣获中兴通讯“最佳服务支持奖”

judy 在 周三, 11/13/2024 - 11:18 提交

在本次中兴通讯全球合作伙伴大会上,紫光同创还凭借卓越的服务支持与技术创新实力,成功荣获中兴通讯“2024年度最佳服务支持奖”

在本次中兴通讯全球合作伙伴大会上,紫光同创还凭借卓越的服务支持与技术创新实力,成功荣获中兴通讯“2024年度最佳服务支持奖”

AMD 宣布推出第二代 Versal Premium 系列,实现全新系统加速水平,满足数据密集型工作负载需求

使用RFSoC(射频系统级芯片)制作适用于OTFS(正交时频空)信号的高动态时延多普勒信道模拟仿真器的原因

随着两大EDA巨头英特尔和AMD于几年前分别被Altera和Xilinx收购之后,笔者不少人一样,认为FPGA将进入冰河时期

本书既是使用Zynq MPSoC的开发人员的实用指南,同样也是希望熟悉器件及其相关设计方法的技术人员的有效参考资料。

通过收购 Flex Logix,ADI 显著增强了数字产品组合

我们正在进入一个多频天文学的新时代,在这个时代,同时观测不同类型的无线电波增进了我们对宇宙的理解,其效果远超观测单一类型的无线电波所能达到的效果

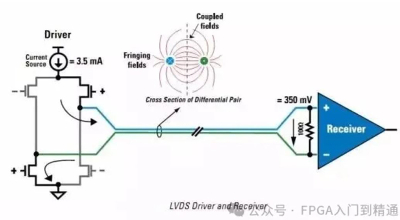

今天继续分享常用的电平标准,并分享电平标准使用注意事项。

作为一名FPGA工程师,经常需要在多个FPGA设备之间移植项目,核心的问题是IP的管理和移植,今天通过安装和使用 FuseSoC 在多个 AMD FPGA 之间移植

在 Teardown 专区开发板主题分享环节,芯驿电子销售总监丁百成带来《FPGA+GPU 异构视频图像处理开发平台 Z19-M 产品分享》。