赋能数字中国建设: 正运动技术联手 Xilinx 展示工业互联智能运动控制器方案

judy 在 周二, 05/07/2019 - 10:52 提交

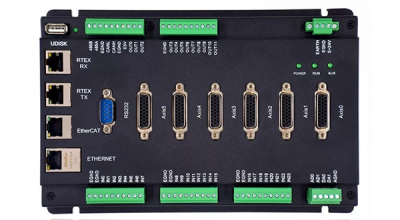

深圳市正运动技术携手自适应和智能计算的全球领先企业赛灵思公司,以及其他基于赛灵思技术提供各种智能方案和产品的业界领先企业一起,共同参展于2019年5月6-8日在中国福州举行的数字中国建设峰会2019。深圳市正运动技术作为智能制造的代表,为与会者展示了3-128轴EtherCAT/RTEX总线的工业互联智能运动控制器的解决方案。

深圳市正运动技术携手自适应和智能计算的全球领先企业赛灵思公司,以及其他基于赛灵思技术提供各种智能方案和产品的业界领先企业一起,共同参展于2019年5月6-8日在中国福州举行的数字中国建设峰会2019。深圳市正运动技术作为智能制造的代表,为与会者展示了3-128轴EtherCAT/RTEX总线的工业互联智能运动控制器的解决方案。

5月6日-9日,自行科技联合全球自适应和智能计算领导企业,赛灵思公司,及其智能产品与方案合作伙伴,共同参加第二届数字中国建设峰会与成果展。公司携国内首款基于深度学习技术的高性能前装量产驾驶员监控系统(DMS)和集成像素级语义分割/雷达融合技术的前向ADAS系统重磅亮相!

作为国内专业的元器件本土代理商和自适应和智能计算的全球领先企业赛灵思公司 (Xilinx, Inc.) 中国唯一的本土代理商,科通集团 携手赛灵思携手多家在不同智能应用领域领先的用户带来各种优秀产品及方案,共同参加:2019年5月6-8日在中国福州举行的数字中国建设峰会2019

预防医学与微创外科手术的发展正在推动内窥镜系统增强功能需求的发展。传统多芯片实现方案会产生时延问题,会对现代内窥镜所需的低延时、高带宽及计算密集型功能造成负面影响。一款典型的内窥镜系统包括具有光源和摄像机头的内窥镜、摄像机控制单元 (CCU) 以及图像管理单元。

MYD-C7Z020 开发板的构建基于 MYC-C7Z020 CPU 模块,该模块是一款基于 ZYNQ 的、Linux 就绪型的小巧 SOM,全面结合 Xilinx XC7Z020-1CLG400C SoC 器件、1GB DDR3 SDRAM、4GB eMMC、32MB 四路 SPI 闪存、千兆位以太网 PHY、USB PHY 和外部看门器

安富利携手自适应和智能计算的全球领先企业赛灵思公司 ,以及其他基于赛灵思技术提供各种智能方案和产品的业界领先企业一起,共同参展于2019年5月6-8日在中国福州举行的第二届数字中国建设峰会。

工业以太网—实时以太网—在过去几年中经历了巨大的增长。虽然经典的现场总线仍大量存在,但它们已经过了巅峰期。流行的实时以太网协议扩展了以太网标准,可以满足实时功能的要求。现在,TSN为实时以太网提供了一条新的途径。

在 MWC19,Xilinx 使用 Xilinx Alveo卡(运用 OvS 加速和遥测技术)与我们在 Barefoot 的合作伙伴展示了应用级加速。

随着射频 (RF) 数据转换器的问世,情况发生了变化。我们现在已经将世界一流的 RF ADC 和 DAC 集成到 Zynq UltraScale +架构中了。因此,传统的射频和模拟工程师不可避免地以前所未有的方式接触到了嵌入式系统

随着新工科建设的工作开展,传统数字基础课程内容的改革变得越来越迫切。一线的老师苦恼于无法抽出时间比较系统而有效地学习和进修面临的新技术。为满足老师们学习新技术的需求,依元素科技开展每月一次的FPGA师资周末集训营,现应参加教师要求加开FPGA师资进阶集训班,时间定为2019年5月18-19日,现开始报名~