MIPI系列之“初识MIPI”

judy 在 周四, 01/10/2019 - 10:31 提交

该系列文章介绍MIPI系列规范。本篇为第一篇,主要介绍MIPI Alliance及其推出的一系列规范,以及相关的一些应用,以便对MIPI有一个全面的了解。后续会针对每一个部分进行详细介绍。

1、MIPI Overview

该系列文章介绍MIPI系列规范。本篇为第一篇,主要介绍MIPI Alliance及其推出的一系列规范,以及相关的一些应用,以便对MIPI有一个全面的了解。后续会针对每一个部分进行详细介绍。

1、MIPI Overview

DDS直接数字式频率合成器(Direct Digital Synthesizer)。本文实现一个具有可以频率可调、相位可调的正余弦、方波、三角波的DDS。

使用 Vivado 设计套件中的各种设计分析特性。

内核重置应该保持断言状态,直到相关时钟稳定为止。在从重置中取出以太网 IP 核之前,它必须具有稳定的频率而且没有故障。 这适用于 SerDes 时钟和 IP 核时钟。 如果在一个时钟中检测到后续不稳定性,就必须重置 100G 以太网 IP 核。

基于 FPGA 的加速原理

很多使用ZCU106/104开发板的小伙伴,发现在官网上可以找到包括IPI,MIG,PCIe等参考设计,但是如何把VCU用起来的流程设计,Target Reference Design(以下简称TRD)不知道哪里去下,那么最新版本的TRD去哪里获得呢?

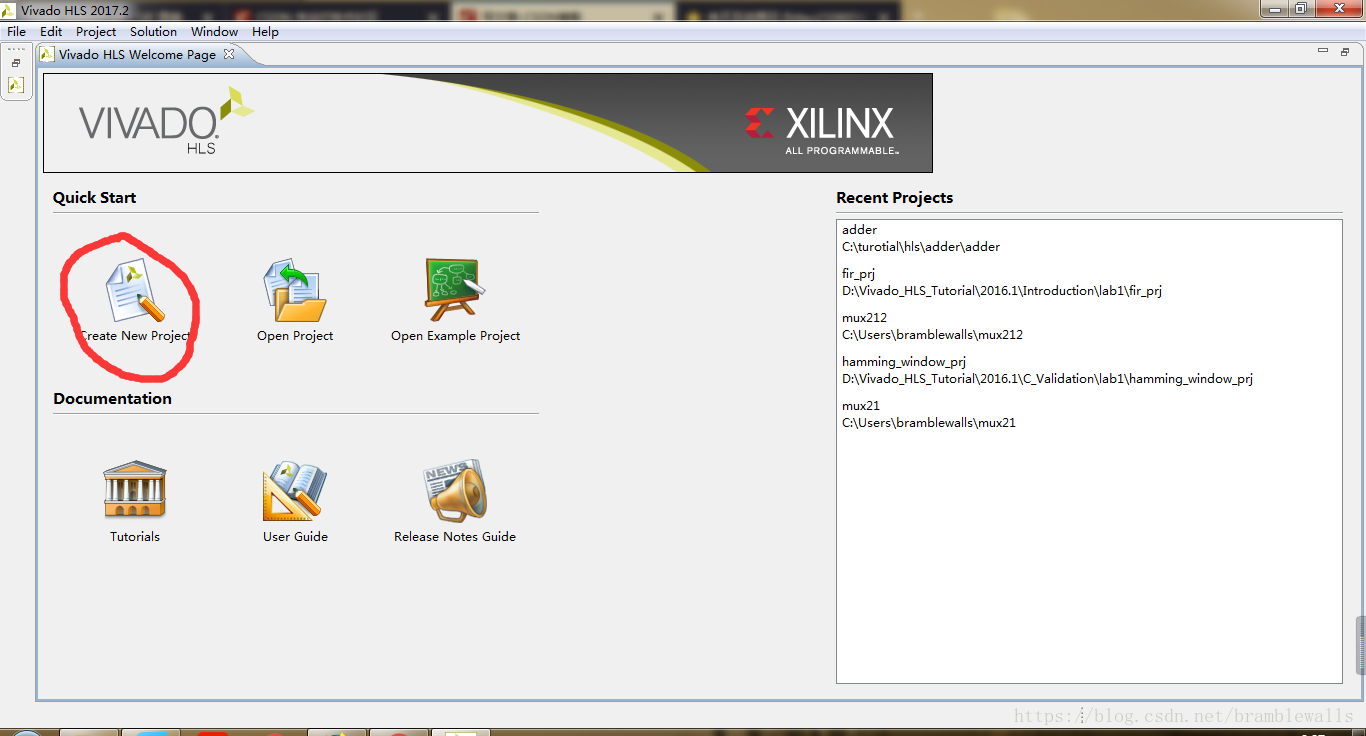

一、用HLS生成一个定制IP(加速器)

(1)首先打开vivado hls,本人的版本是2017.2,点击创建一个新工程。

(2)设置工程名和路径,顶层函数设置为add,创建一个新的C++程序,名字叫做adder.cpp,不用在testbench中添加文件。

选择板子的时候搜索xc7z020clg400-1,这是PYNQ的板子号,选择完成。

视频演示了 DDR3 内存的 Kintex-7 FPGA 接口功能。

前面我们介绍了按键中断,其实我们稍作修改就可以用按键控制LED了。做个小实验,两个按键分别控制两个led亮灭。

板子:zc702。

硬件部分

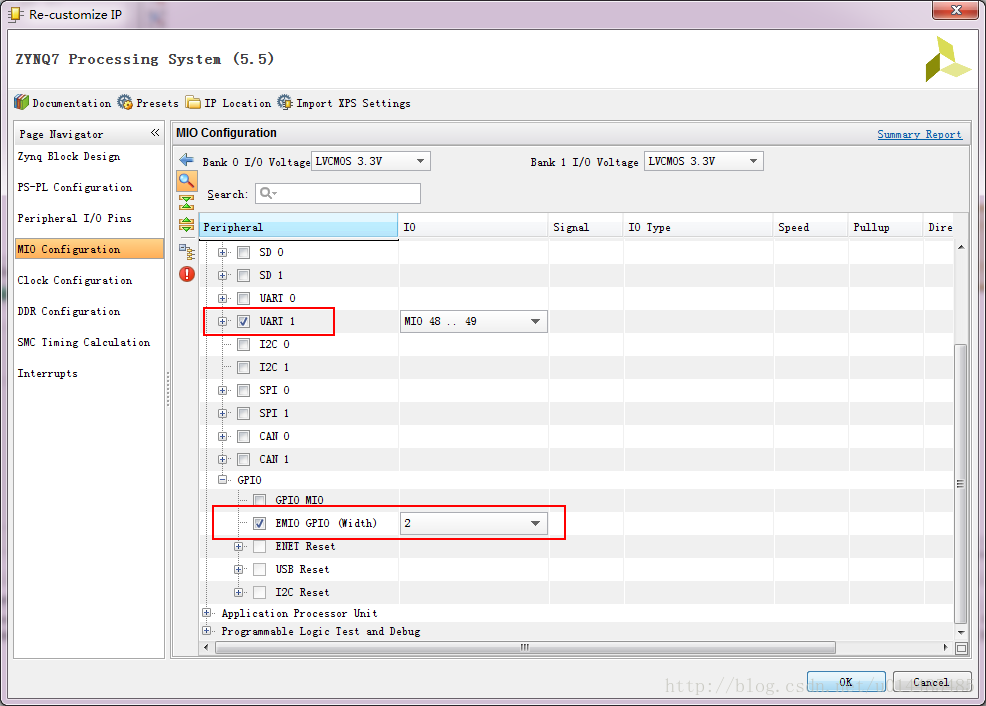

添加zynq核:

勾选串口用于打印信息,勾选EMIO,我们控制两个led,所以需要2bit

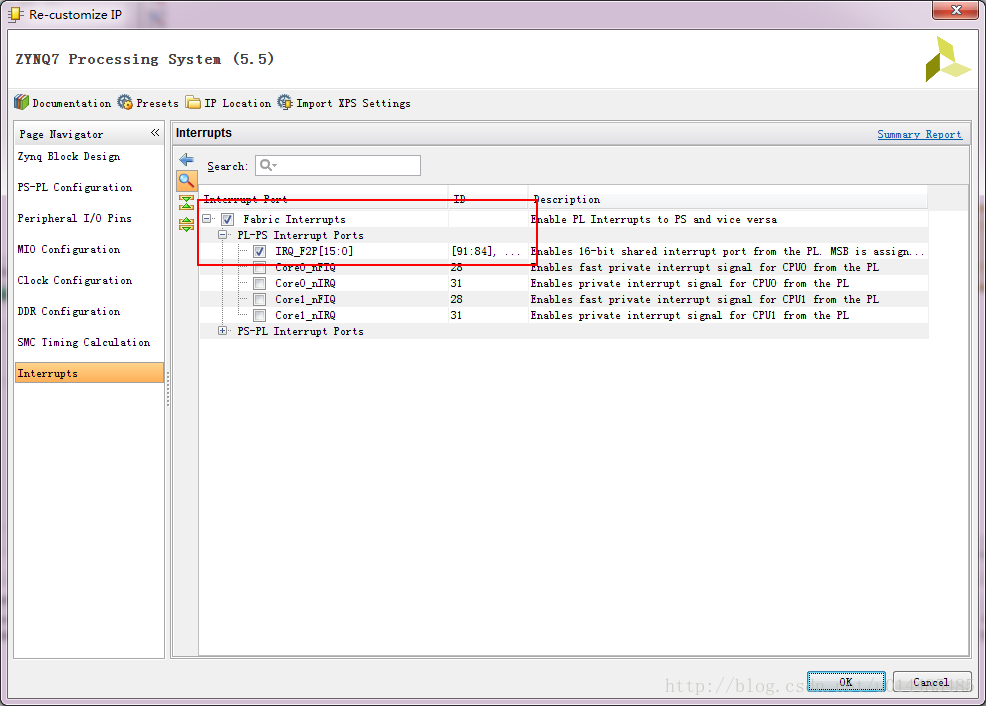

PL 到PS的中断勾选上:

PL时钟什么的都用不到,我们用的按键不需要时钟,EMIO属于PS。

再添加一个concat IP用于合并两路按键信号:

为了复用现有的MATLAB®代码,LabVIEW Communications System Design Suite (LabVIEW Comms) 新增了MATLAB专用接口的功能。无线原型的开发者可使用已有的MATLAB函数或脚本,将其连接至LabVIEW Comms在Windows处理器上运行的代码部分