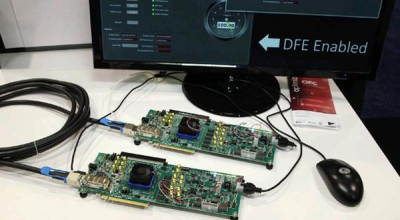

在多通道宽带射频系统中通过低压差分信号传输数据总线实现大型射频数据共享

judy 在 周二, 01/22/2019 - 10:15 提交

现今,使用FPGA技术进行射频数据信号处理已经非常普遍,因为该技术可实现高速计算能力。通常情况下,处理大量RF数据需要部署的FGPA资源越来越多。因此,FPGA模块会跨多个处理子系统进行部署。借助FlexRIO FPGA模块和LVDS数字接口模块,ST Kinetics成功地设计并实现了一个解决方案

现今,使用FPGA技术进行射频数据信号处理已经非常普遍,因为该技术可实现高速计算能力。通常情况下,处理大量RF数据需要部署的FGPA资源越来越多。因此,FPGA模块会跨多个处理子系统进行部署。借助FlexRIO FPGA模块和LVDS数字接口模块,ST Kinetics成功地设计并实现了一个解决方案

在介绍ODDR之前,我们先简单了解一下OLOGIC。OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。OLOGIC 资源的类型有OLOGIC2(位于HP I/O banks)和OLOGIC3(位于HR I/O banks)。

以太网融合已成现实。以太网起源于非关键型计算机网络,已成为工业自动化、交通运输以及航空航天/国防的标准。以太网交换机为动态扩展增加了灵活性。基于 ARM 并支持可扩展以太网交换机的多核处理器恰好具有所需的基础架构&灵活应变。非常适合您的应用,不大不小,而且成本正好

最近入手了 UltraZed-EG PCIe Carrier Card ,这是一款基于 UltraZed-EG 核心板进行延伸的开发板,和 Zybo Board 类似,是一款同时具有 Xilinx FPGA 并且包含了 ARM CPU 的开发平台。为了了解这块开发板,我做了一些整理,让我们一样从硬件以及外围开始吧~

阿里云FaaS平台创新及应用场景

本文主要介绍以太网Line Side对外接口,也被称为MDI(Media Dependent Interface),包括电口和光口。其中光模块主要针对10G以下的,10G以上的本文就不做介绍了。

前面的中断学习中我们学了按键,GPIO,Timer,是时候把它们整合到一起了。今天我们混合使用PS/PL部分的资源,建立一个比较大的系统

视频演示将展示 Xilinx 16nm Virtex UltraScale+ FPGA,其所集成的 100G 以太网 MAC 和 RS-FEC 能够串行工作,通过极具挑战的电子或光学互连发送数据。集成可节省逻辑区域,简化实现方案,并可降低日益普及的 100G 以太网接口或高速背板应用上的功耗

Zynq7000 系列芯片有 54 个 MIO(multiuse I/O), 它们分配在 GPIO 的 Bank0 和Bank1 隶属于 PS 部分, 这些 IO 与 PS 直接相连。 不需要添加引脚约束, MIO 信号对 PL部分是透明的。 所以对 MIO 的操作可以看作是纯PS 的操作

本文主要介绍Xilinx FPGA的配置模式,主要包括Master/Slave模式,Serial/SelectMAP模式,JTAG模式等。其中7系列只有Logic部分,其配置相关功能引脚全部连接到FPGA端的特定bank上;Zynq 7000系列既有PL部分,也有PS部分,其JTAG从PL侧引出,其余配置相关引脚全部从PS侧引出