【XDF资料下载】基于FPGA的视频图像特征识别和对比

judy 在 周四, 01/31/2019 - 09:59 提交

基于FPGA的视频图像特征识别和对比

基于FPGA的视频图像特征识别和对比

当面对一个项目计划时,你最后一次听到“需要多长时间就花多长时间”或者“如果第一次不成功,不要担心,你总能搞定的”这些话大概是什么时候的事?很可能从来就没有过。随着FPGA变得越来越强大,处理的任务范围也越来越广,缩短设计周期并且最小化风险变得前所未有的重要

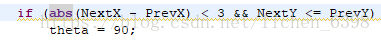

在viado SDK的程序开发中会出现以下的问题

出现问题的原因可能是

没有添加对应的头文件

解决办法:添加对应的头文件 如上图:添加#include”stdlib.h”

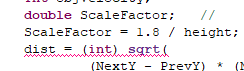

没有添加库函数

解决的方法是:

点击工程文件,右键,选择Properties

如下图:

选择 C/C++ Build 下的Setting 选择:Libraries 添加m文件 因为abs()位于math.h函数里

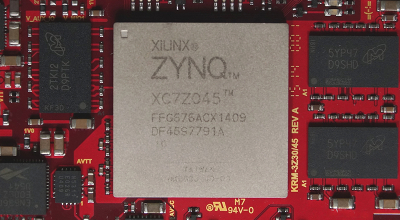

背景:ZynqNet能在xilinx的FPGA上实现deep compression。

目的:读懂zynqNet的代码和论文。

一、网络所需的运算与存储

1.1 运算操作:

1.2 Memory requirements:

1.3 需求分析:

戴姆勒的 Thomas Kaelberer 介绍了 MBUX 车内助手 (MBUX Interior Assistant),这是新款梅赛德斯 GLE 运动型多用途车中首款人工智能解决方案。Xilinx 平台的选择是因为其可针对车辆顶部热约束计算子系统位置提供最佳性能功耗比和最低时延

在介绍Gateway In block时谈到了System Generator中的数据类型,及不同的量化和溢出方式。本文将以两个简单的设计实例,更直观地说明不同的量化和溢出方式有什么区别。

本PPT介绍了高效使用云计算来进行 FPGA 设计和性能优化。

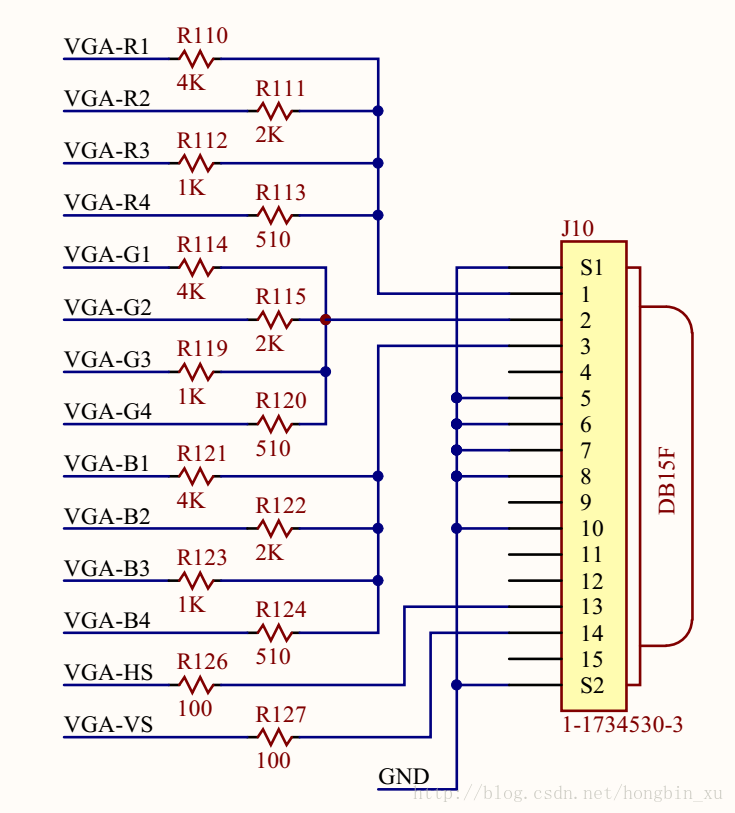

VGA硬件接口

到zedboard官方给出的原理图中查看:

RGB信号,各四位;这里的设计是使用了电阻分压模拟了DAC芯片实现了4X4X4的RGB信号,如果要更好的显示效果还是建议使用专门的DAC。

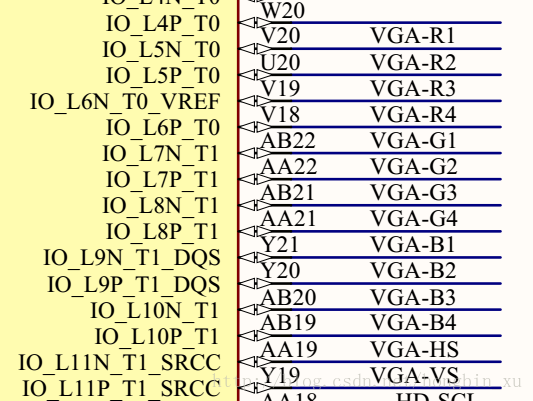

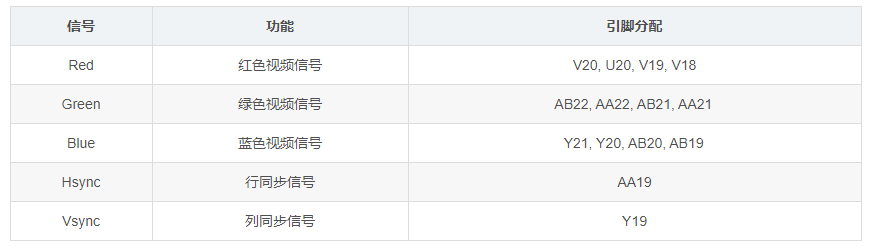

上面给出了所有的引脚分配。

VGA时序分析

DeePhi 在 Xilinx FPGA 上使用 DeePhi 技术演示 SSD算法

在网上看了很多的介绍,基本都是一样的,但是根据这些博客,自己验证了下发现结果和matlab中不一样。

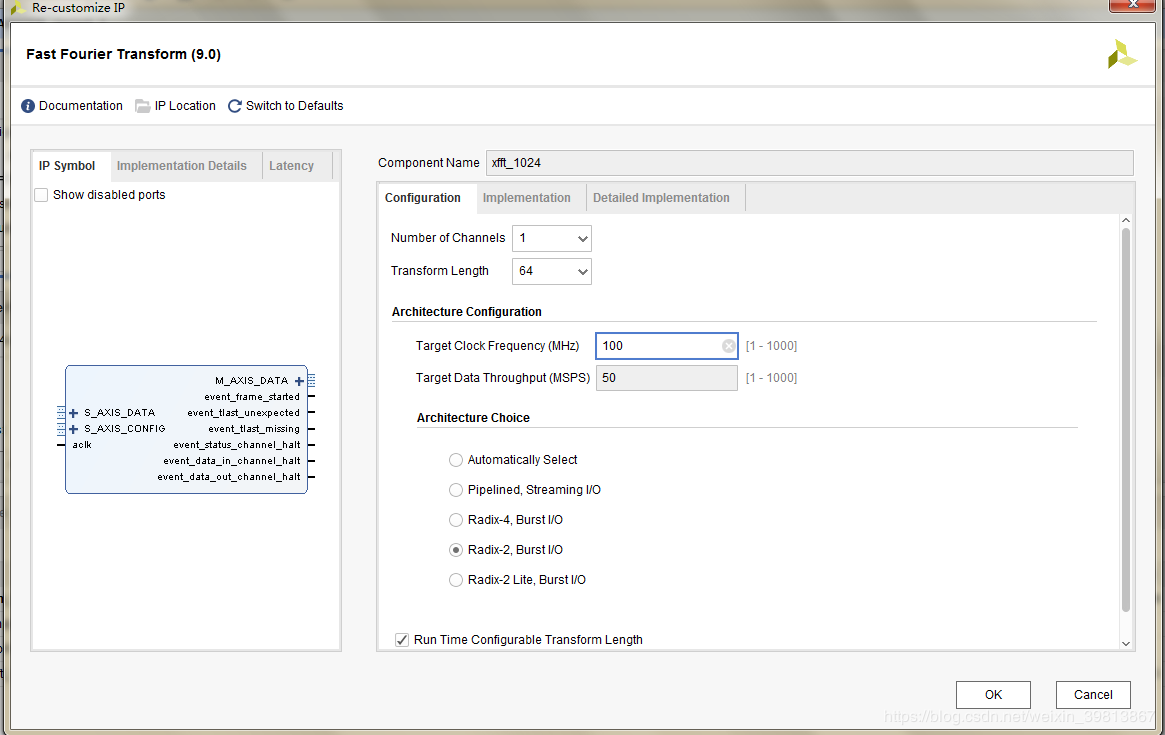

1.配置IP核

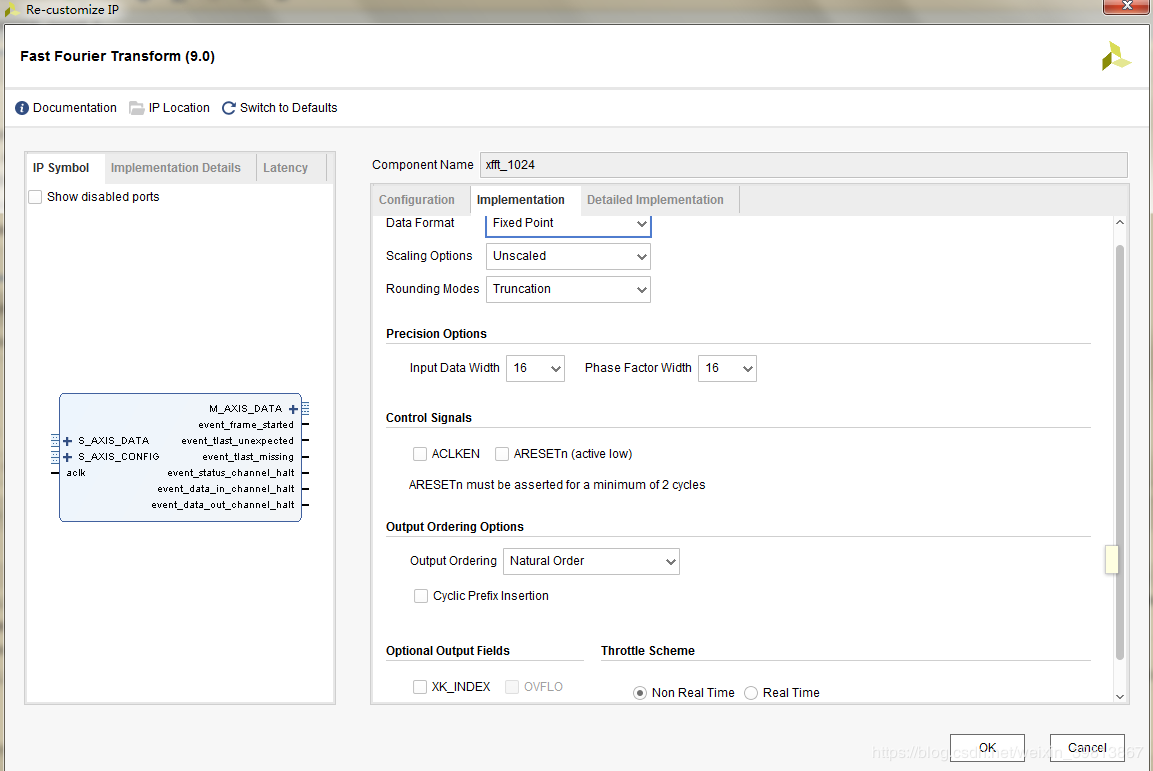

用vivado17.2 IP版本为9.0,配置首先配置最大长度为64,时钟为100MHz,将长度可以改变选中,如下图所示:

进一步的配置,设置数据为整型,未缩放,输入16bit,输出自然顺序(不然虚部不方便验证)。

第三页默认