Xilinx ZYNQ UltraScale+系列连载之写在前面

judy 在 周四, 02/14/2019 - 10:56 提交

FPGA 是可编程芯片,因此FPGA 的设计方法包括硬件设计和软件设计两部分。硬件包括 FPGA 芯片电路、存储器、输入输出接口电路以及其他设备;软件即是相应的 HDL 程序以及最新非常流行的基于高层次综合的程序方法

FPGA 是可编程芯片,因此FPGA 的设计方法包括硬件设计和软件设计两部分。硬件包括 FPGA 芯片电路、存储器、输入输出接口电路以及其他设备;软件即是相应的 HDL 程序以及最新非常流行的基于高层次综合的程序方法

tcl语法

(1)if 判断,{}中的语句需要用[]括起来

if {} { 必须留在这一行

}

elseif而不是else if

(2)注释单起一行,不要在命令末尾

(3)procedure的参数用空格隔开

(4)file exists判断文件是否存在

ZynqNet能在xilinx的FPGA上实现deep compression的网络。目的:读懂ZynqNetCPU端的代码。

Vivado综合工具支持直接在RTL文件或XDC文件中设置综合属性。如果Vivado识别出设置的属性,会创建与之相关的逻辑电路;如果不能识别设置的属性,会将该属性和值存放在生成的网表中。因为某些属性,比如LOC约束适用于布线过程,因此必须保留该属性配置情况

数据中心 AI 加速 — Xilinx ML 套件

赛灵思公司宣布已将完整的 HDMI 2.1 IP 子系统引入其知识产权核(IP核)产品组合中,使得各种搭载赛灵思器件的专业音视频设备能够发送、接收和处理高达 8K(7680x4320 像素)的超高清 (UHD) 视频

在HLS中使用帧间差分法生成了IP核,这里讲述如何在vivado中调用IP core

在这篇文章,我们要讲的则是如何透过 AXI_GPIO 来处理 输入 的控制,并让 Cortex-R5 根据不同的输入,在 ps_uart1 输出不同的讯息,以及控制不同的 LED 亮暗。

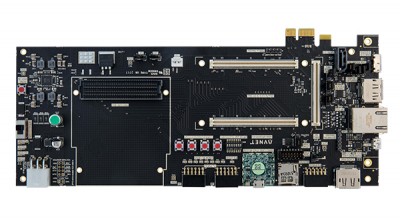

本文档提供了 Xilinx Alveo 数据中心加速器卡的软硬件安装全流程指南。 Avelo 卡符合 PCIe Gen3 x16 规范并采用赛灵思 UltraScale+ 架构,完美适用于加速计算密集型应用,比如数据库加速、机器学习、数据分析以及视频处理等。

Falcon Computing 公司在 XDF 硅谷推出混合云 GATK 管道的 FPGA 加速