UltraZed-EG PCIe Carrier Card 开发纪录: Hello Cortex-A53

joycha 在 周一, 01/28/2019 - 10:16 提交

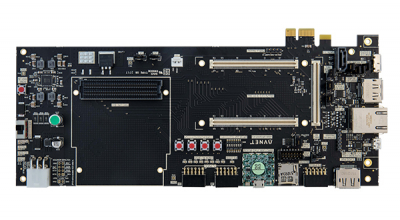

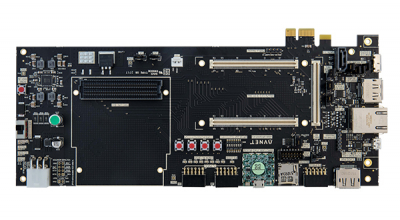

在这篇文章中,我们将让这块开发板的 Cortex-A53 透过 AXIO_GPIO 模块,点亮板子上的 LED 灯,并且透过 ps_uart0 输出一些讯息。

在这篇文章中,我们将让这块开发板的 Cortex-A53 透过 AXIO_GPIO 模块,点亮板子上的 LED 灯,并且透过 ps_uart0 输出一些讯息。

本篇主要介绍MIPI物理层规范中的D-PHY,主要包括D-PHY的架构、操作模式、电气特性等。

在读取 IBERT 的自适应环路代码时,出现了与 DMONITOROUT 的期望值不同的值。

利用XilinxISE软件开发FPGA的基本流程包括代码输入、功能仿真、综合、综合后仿真、实现、布线后仿真与验证和下班调试等步骤。如下图所示

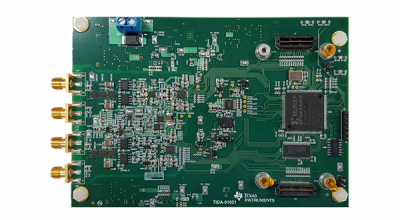

TIDA-01051 参考设计用于演示极高通道数数据采集 (DAQ) 系统(如用在自动测试设备 (ATE) 中的系统)经过优化的通道密度、集成、功耗、时钟分配和信号链性能。利用串行器将多个同步采样 ADC 输出与几个 LVDS 线结合

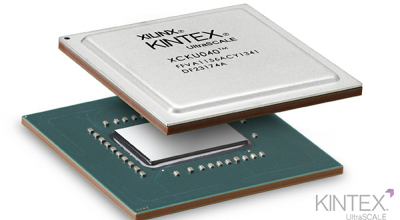

FPGA编译与加速的未来

一开始接触到FPGA,肯定都知道”复位“,即简单又复杂。简单是因为初学时,只需要按照固定的套路——按键开关复位,见寄存器就先低电平复位一次,这样一般情况可以解决99%的问题,甚至简单的设计,就不可能有问题。复杂是因为复位本身是对大规模的硬件单元进行一种操作,必须要结核底层的设计来考虑问题

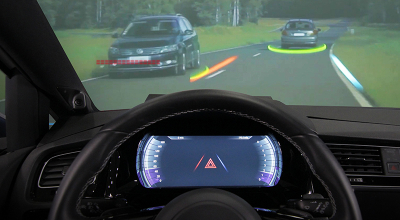

2018年,汽车行业对于自动驾驶关键技术和产品落地的探索仍在持续,而且一些Global Tier1和OEM仍在重金投入,但面对L3+级别自动驾驶系统的超高难度和复杂度,尤其在量产中众多的已见以及尚未可知的困难时,人们对自动驾驶产业成熟的预期在逐渐归于理性,整个行业某种程度上开始了新一轮的反思和探讨

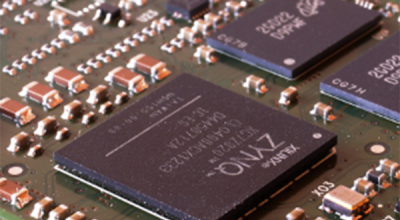

zynq 的内嵌了 XADC,可以用来采集电压;

Temp:芯片温度

VCCINT: 内部PL核心电压

VCCAUX: 辅助PL电压

VCCBram: PL BRAM电压

VCCPInt: PS内部核心电压

VCCPAux: PS辅助电压

VCCDDR: DDR RAM的工作电压

VREFP: XADC正参考电压

VREFN: XADC负参考电压

1、新建工程,添加block design。添加zynq7 processor和xadc模块。

2、Run Block Automation后会自动配置zynq7处理器;Run Connection Automation 会自动将模块进行连接,将xadc模块挂载在axi总线下,这样xadc的相关寄存器会映射到处理器的内存(DDR)上。自动添加的两个模块,一个用于管理全局复位,一个用于同步axi总线。

1. Python 的特点和优点是什么?

答案:略。

2. 什么是lambda函数?它有什么好处?