UltraZed-EG PCIe Carrier Card 开发纪录: 硬件认识

joycha 在 周一, 01/21/2019 - 16:02 提交

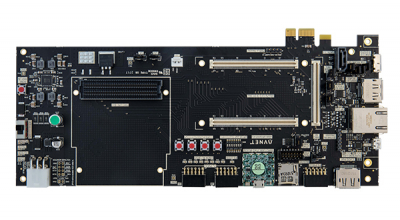

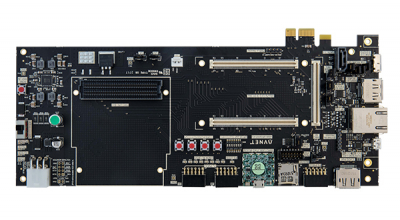

最近入手了 UltraZed-EG PCIe Carrier Card ,这是一款基于 UltraZed-EG 核心板进行延伸的开发板,和 Zybo Board 类似,是一款同时具有 Xilinx FPGA 并且包含了 ARM CPU 的开发平台。为了了解这块开发板,我做了一些整理,让我们一样从硬件以及外围开始吧~

最近入手了 UltraZed-EG PCIe Carrier Card ,这是一款基于 UltraZed-EG 核心板进行延伸的开发板,和 Zybo Board 类似,是一款同时具有 Xilinx FPGA 并且包含了 ARM CPU 的开发平台。为了了解这块开发板,我做了一些整理,让我们一样从硬件以及外围开始吧~

阿里云FaaS平台创新及应用场景

本文主要介绍以太网Line Side对外接口,也被称为MDI(Media Dependent Interface),包括电口和光口。其中光模块主要针对10G以下的,10G以上的本文就不做介绍了。

前面的中断学习中我们学了按键,GPIO,Timer,是时候把它们整合到一起了。今天我们混合使用PS/PL部分的资源,建立一个比较大的系统

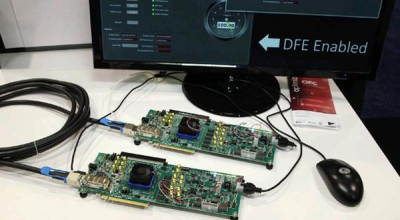

视频演示将展示 Xilinx 16nm Virtex UltraScale+ FPGA,其所集成的 100G 以太网 MAC 和 RS-FEC 能够串行工作,通过极具挑战的电子或光学互连发送数据。集成可节省逻辑区域,简化实现方案,并可降低日益普及的 100G 以太网接口或高速背板应用上的功耗

Zynq7000 系列芯片有 54 个 MIO(multiuse I/O), 它们分配在 GPIO 的 Bank0 和Bank1 隶属于 PS 部分, 这些 IO 与 PS 直接相连。 不需要添加引脚约束, MIO 信号对 PL部分是透明的。 所以对 MIO 的操作可以看作是纯PS 的操作

本文主要介绍Xilinx FPGA的配置模式,主要包括Master/Slave模式,Serial/SelectMAP模式,JTAG模式等。其中7系列只有Logic部分,其配置相关功能引脚全部连接到FPGA端的特定bank上;Zynq 7000系列既有PL部分,也有PS部分,其JTAG从PL侧引出,其余配置相关引脚全部从PS侧引出

在本次研讨会中,赛灵思专家将向您介绍赛灵思MicroBlaze 处理器将如何让启动新设计变得前所未有地简单快捷!无需 RTL 经验就能使用 Vivado IP 集成器工具以及第三方 IP 库。专家将为您演示如何使用外围设备在几分钟之内快速打造任何嵌入式设计原型

可靠的通用通信是工业物联网 (IIoT) 的基础。低时延、高带宽、恢复力、可扩展性及符合标准是关键。自动化现已跨越 40 多个协议,可满足众多目标应用的特定需求。可编程逻辑为您的产品匹配所有客户网络带来的灵活性是无与伦比的

深度学习软硬一体化加速方案,具备模型剪枝&量化加速工具,能将原始模型性能提升 4 倍以上。高性能的加速引擎提供 2.4Tops 的强大 AI 算力,完整的嵌入式参考设计,便于硬件产品的结构设计及二次开发。AI 硬件产品通过集成 EdgeBoard,可大大提升终端设备 AI 推理能力。