快速部署原型验证:从子卡到调试的全方位优化

judy 在 周日, 09/29/2024 - 15:12 提交

在原型验证过程中,"bring-up" 是一个关键阶段,涉及一系列操作,从硬件配置、基本功能验证到复杂系统的运行调试

在原型验证过程中,"bring-up" 是一个关键阶段,涉及一系列操作,从硬件配置、基本功能验证到复杂系统的运行调试

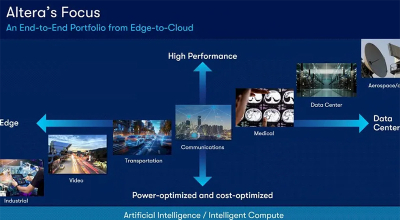

Altera在年度开发者大会上公布了下一代能效与成本优化的Agilex™ 3 FPGA情况,并宣布针对Agilex 5 FPGA提供新的开发套件和软件支持

随着人工智能技术的飞速发展,数据中心的架构变得更加精细和复杂,这对网络的加速设计和数据处理能力提出了更高的标准

高云半导体自2019年发布第一颗FPGA车规芯片至今,在汽车市场持续发力,先后发布了10余颗车规芯片,逻辑容量从1K~138K

在汽车电子应用展中,紫光同创展示了车规FPGA芯片领域最新成果PGL25GA器件,该芯片已获AEC-Q100 Grade 2车规认证并上市发布

该方案采用 ALINX 基于紫光同创 PG2K400 FPGA 芯片设计开发的 K401 核心板和 AXK401 开发板,可高效实现车载摄像头视频数据的采集与注入

FIR滤波器是数字信号处理中常用的滤波器,除了通过Verilog代码自己实现外,Vivado提供了一个FIR滤波器 IP,可以直接调用。

就像十多年前一样,我们对数据中心三重混合系统的前景充满热情。我们坚信 CPU、GPU 和 FPGA 在复杂且高性能的系统中都有一席之地

随着大型语言模型(LLM)和生成式AI的激增,行业正在努力解决这些基于云的AI应用处理大数据以及训练和部署高级AI模型所需的密集计算能力。

Altera最新发布的Agilex 3 FPGA系列吸引了行业内广泛关注,这不仅是因为其出色的硬件设计,还在于它针对嵌入式应用提供了高效的AI推理支持和安全保障