YunSDR通信小课堂(第34讲)

judy 在 周四, 04/10/2025 - 09:58 提交

在设计RFSoC PS时,必须选择合适的软件堆栈来满足设计要求。软件栈是一组基本软件,开发人员可以在这些软件的基础上添加他们自己的定制软件

在设计RFSoC PS时,必须选择合适的软件堆栈来满足设计要求。软件栈是一组基本软件,开发人员可以在这些软件的基础上添加他们自己的定制软件

智多晶的 LWIP 通信系统就像是一台双核驱动的高性能引擎,搭载在EVAL-SA5Z-30-D1-8U213C开发板上,SA5Z-30芯片中集成CM3微处理器和FPGA

在MIPI多路摄像头拼接项目中,需要使用到FIFO的IP核来进行数据的缓存与时钟域的交互,下面我来介绍一下Diamond FIFO IP核生成与例化的步骤。

北格逻辑的 Keystone 梯形校正 IP,借助高效的数字图像预处理技术,成功构建了光学失真与数字补偿的闭环系统。

随着近来Deepseek的横空出世,降低算力需求,为RISC-V带来了更多的创新机遇。RISC-V计算架构搭乘上AI时代的快车

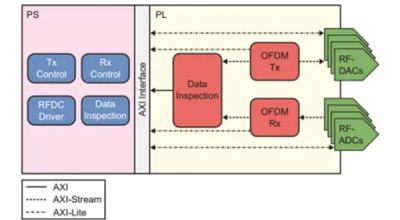

RFSoC器件分为两个主要的可定制部分,处理系统(PS)和可编程逻辑(PL)。在为RFSoC设计系统时,值得首先考虑的是设计的功能如何在这两个元素之间进行划分

设备树(Device Tree)是一种数据结构,用于描述计算机硬件组件,以便操作系统内核能够识别和管理这些组件。

本应用简报重点介绍了DS90LVRA2-Q1,这是一种支持低至 1.8V I/O 电压的外部 LVDS 接收器解决方案。

在AI算力需求爆炸、数据中心加速迭代的当下,FPGA的战场正从“逻辑密度”转向“内存带宽”。英特尔旗下Altera公司近日宣布,其Agilex 7 FPGA M系列正式量产出货

2025紫光同创FPGA技术研讨会以“芯智融合·同创未来”为主题将重磅发布高性能、多核异构SoPC等系列新产品,赋能工业自动化、图像视频、智能汽车等场景创新!