基于Xilinx的时序分析与约束(1)——什么是时序分析?什么是时序约束?什么又是时序收敛?

judy 在 周三, 07/27/2022 - 11:51 提交

这个专栏,我会从时序分析、时序约束和时序收敛3个方面来一起学习基于Xilinx FPGA和Vivado开发平台的FPGA时序相关内容。

这个专栏,我会从时序分析、时序约束和时序收敛3个方面来一起学习基于Xilinx FPGA和Vivado开发平台的FPGA时序相关内容。

《UltraFast 设计方法时序收敛快捷参考指南》提供了以下分步骤流程, 用于根据《UltraFast设计方法指南》( UG949 )中的建议快速完成时序收敛:

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对齐进行了整理,分为了几篇文章。

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对齐进行了整理,分为了几篇文章。

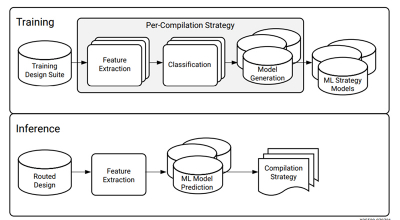

本白皮书描述智能设计如何使用机器学习和基于规则的系统来模拟时序收敛专家并提高生产力。

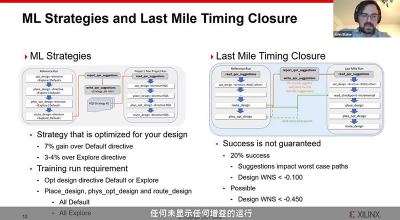

本会议将介绍可帮助大家解决棘手时序问题的时序收敛辅助工具。

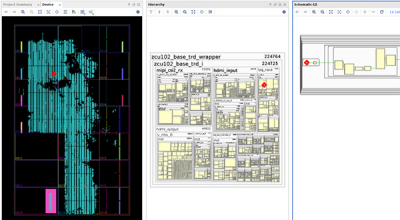

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整设计中提取目标模块、对其进行布局规划、约束,然后通过实现工具来运行这些模块,以判断是否能够独立达成时序收敛。

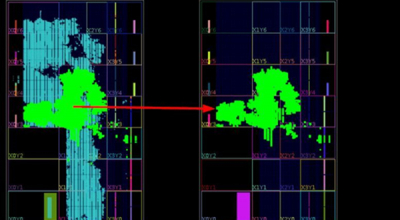

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

本文档旨在描述推荐的设计方法,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

本文描述了用于实现赛灵思 FPGA 器件资源的有效利用以及在 Vivado® Design Suite 中加速设计实现和时序收敛的推荐设计方法论。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。