基于边缘应用开发的Xilinx AI 解决方案

judy 在 周一, 08/26/2019 - 10:46 提交

本课程介绍如何在边缘计算平台上使用DNN算法、模型、推理、训练以及框架。

本课程介绍如何在边缘计算平台上使用DNN算法、模型、推理、训练以及框架。

经常听到有媒体问ASIC是否取代FPGA这类问题,看看ASIC设计流程,其中的数字前端中的仿真和验证是离不开FPGA的,所以FPGA和ASIC是共生关系,有了更大的FPGA ,才能在数字IC仿真原型设计效率上大大提升,才可以支持和设计更复杂更大的ASIC,近10年来,赛灵思一直保持着最大业内FPGA的记录,今天,赛灵思再次刷新最大FPGA的新记录

Aupera Technologies 是数据中心视频处理系统领域的新兴企业。Aup2600 是一种专用分布式视频处理系统,内置 48 个赛灵思 Zynq® UltraScale+™ MPSoC。此外,Aup2600 还提供基于赛灵思 Vivado 环境的完整视频 +AI 软件框架和用于神经网络处理的深度学习处理器单元 (DPU)。

在 2019 年 8 月 22 - 23日,2019全球闪存峰会上,赛灵思作为 FPGA 的发明者将现场展示我们的 “基于 FPGA 的 NVMe Target 控制器” 解决方案。同期在闪存存储网络论坛上,赛灵思公司数据中心架构师,唐杰也将做《FPGA 助力计算和存储的结合》的主题演讲,与参会者共同探讨新的大数据时代,计算和存储所面临的新挑战和新趋势

自适应和智能计算的全球领先企业赛灵思公司今天宣布推出全球最大容量的 FPGA – Virtex UltraScale+ VU19P,从而进一步扩展了旗下 16 纳米 (nm) Virtex UltraScale+ 产品系列。VU19P拥有 350 亿个晶体管,拥有有史以来单颗芯片最高逻辑密度和最大I/O 数量,可用以支持未来最先进 ASIC 和 SoC 技术的仿真与原型设计。

对赛灵思而言,上星期是激动人心的一个星期。业界首款半高半长、可支持 PCIe Gen 4 的自适应加速器卡Alveo U50 正式发布。长约7英寸,宽约2英寸,Alveo U50是小型封装的一大突破。该卡集成 HBM2 高带宽存储器、100Gbps 网络连接和赛灵思 UltraScale+ FPGA 架构

在这篇文章里你可以了解到广告推荐算法Wide and deep模型的相关知识和搭建方法,还能了解到模型优化和评估的方式。我还为你准备了将模型部署到FPGA上做硬件加速的方法,希望对你有帮助

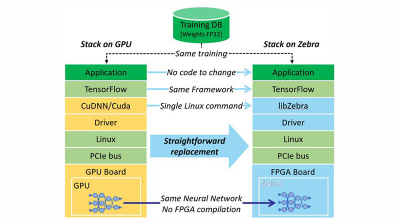

Zebra 可消除深度学习推断中具有挑战性的编程及 FPGA 任务。Zebra 可轻松部署和适应广泛的神经网络及框架。

2019年8月1日至2日,“中国开放指令生态(RISC-V)联盟”(简称CRVA联盟)与鹏城实验室,在湖北恩施举行的中国计算机学会第二十三届计算机工程与工艺学术年会暨第九届“微处理器技术”论坛(NCCET 2019)现场,联合展示了最新研发的RISC-V开源芯片设计系统级验证及原型平台SERVE,介绍开源理念并鼓励参会人员积极参与。

Vitesse Data 的 Deepgreen DB 是一款可扩展的 MPP 数据库解决方案,源于开源 Greenplum 数据库项目,与开源项目完全兼容。 Deepgreen DB 可在本地设备或公共云上无缝工作。AWS F1 实例可使用多达 8 个 FPGA 实例针对总共 64 vCPU 和 976 GB 的内存进行配置。