Zynq中FPGA上电时序

demi 在 周五, 01/03/2020 - 14:25 提交

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO

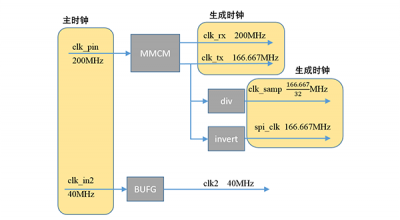

Vivado会自动设别出两个主时钟,其中clk_pin_p是200MHz,这个是直接输入到了MMCM中,因此会自动约束;另一个输入时钟clk_in2没有约束,需要我们手动进行约束。

在 Vivado/ISE 中遇到许可问题时,该怎么办呢?本文介绍了使用不同类型的许可证时可能遇到的不同问题。

AXI4-Lite接口是AXI4的子集,专用于和元器件内的控制寄存器进行通信。AXI-Lite允许构建简单的元件接口。这个接口规模较小,对设计和验证方面的要求更少。

我们以Vivado自带的wave_gen工程为例,该工程的各个模块功能较为明确,如下图所示。为了引入异步时钟域,我们在此程序上由增加了另一个时钟--clkin2,该时钟产生脉冲信号pulse,samp_gen中在pulse为高时才产生信号。

互联结构包括直通模式、只转换模式、N-1互联模式、N-M互联模式。

For 循环是解决问题的瑞士军刀,但是,当需要浏览代码以快速阅读你所做的事情时,它们可能会让人不知所措。有三种技术 — map、filter 和 reduce — 可以通过描述如何进行迭代来代替 for 训练。JavaScript 中也有这些技术,但是在 Python 中的实现略有不同。

在xdc文件中,按约束的先后顺序依次被执行,因此,针对同一个时钟的不同约束,只有最后一条约束生效。虽然执行顺序是从前到后,但优先级却不同;就像四则运算一样,+-x÷都是按照从左到右的顺序执行,但x÷的优先级比+-要高。

“算力”在未来,就像当年的蒸汽机、电力一样,俨然已经是生产力发展的核心要素,也就是说,谁拥有超越别人的“算力”,谁就会拥有更高的生产力和效率,谁也就能在创新上实现真正的突破,成为推动产业和时代进步的原动力。所以“算力”会和“原力”一样成为人们期望拥有的能力。

在上一篇文章中,我们简要介绍了更高层次的问题,这些问题为优化加速器的需求奠定了基础。作为一个尖锐的问题提醒,现在让我们通过一个非常简单的图像分类算法,来看一看与之相关联的计算成本与功耗。