verilog学习之常用语法之状态机

demi 在 周二, 12/17/2019 - 14:02 提交

状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路。通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态的时序逻辑电路,三是输出组合逻辑电路。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路。通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态的时序逻辑电路,三是输出组合逻辑电路。

本文主要介绍FPGA选型时的速度等级这个参数。大家在进行FPGA选型时都会看见一个参数:Speed Grade,这就是芯片的速度等级。

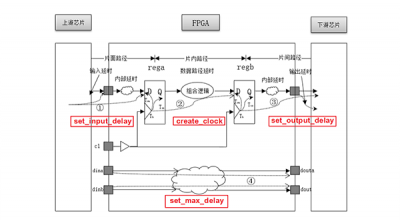

典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。

本文主要介绍Xilinx FPGA的FMC接口。Xilinx FPGA的FMC是FPGA Mezzanine Card的简称。FMC分为处理引擎(载卡)和I/O引擎(FMC模块)两大部分。

有多种类型的时序违例可归类为脉冲宽度违例:最大偏差违例;最小周期违例;最大周期违例;低脉冲宽度违例;高脉冲宽度违例。

什么是时序约束?泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。因此如果我们不加时序约束,软件是无法得知我们的时钟周期是多少,PAR后的结果是不会提示时序警告的。

“要养成良好的Verilog代码风格,要先有硬件电路框图之后再写代码的习惯,设计出良好的时序,这样才能在FPGA开发或者ASIC设计中起到事半功倍的效果,否则会事倍功半。”

本文想针对测试中一种很常见的测试场景,即参数化测试,继续聊聊关于测试的话题,并尝试将这几个测试框架串联起来,做一个横向的比对,加深理解。

有多种类型的时序违例可归类为脉冲宽度违例:最大偏差违例;最小周期违例;最大周期违例;低脉冲宽度违例;高脉冲宽度违例。

回想一下平时我们常用的复位方式:1.首先,上电后肯定是要复位一下,不然仿真时会出现没有初值的情况;2.最好有个复位的按键,在调试时按一下复位键就可以全局复位了;3.也许是同步复位,也许是异步复位,不同的工程师可能有不同的方案。