人工智能引发能源问题,我们该怎么办?(一)

demi 在 周五, 12/27/2019 - 14:04 提交

在 2014 年,斯坦福大学教授 Mark Horowitz 发表了一篇题目为“计算的能源问题(以及我们该怎么办)”的论文。 如果可以的话,我想借用并改编一下 Mark 的论文标题,这样我就可以就机器学习推断应用为什么应该考虑专用硬件,分享一下我的一些观点。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

在 2014 年,斯坦福大学教授 Mark Horowitz 发表了一篇题目为“计算的能源问题(以及我们该怎么办)”的论文。 如果可以的话,我想借用并改编一下 Mark 的论文标题,这样我就可以就机器学习推断应用为什么应该考虑专用硬件,分享一下我的一些观点。

默认情况下,保持时间的检查是以建立时间的检查为前提,即总是在建立时间的前一个时钟周期确定保持时间检查。

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

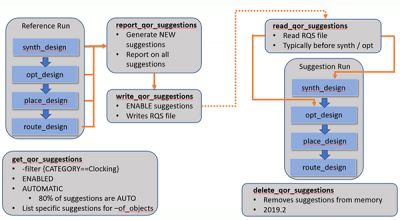

许多 FPGA 设计都难以达成所期望的性能目标。原因不尽相同,以下列出的只是其中部分可能的原因:未遵循 UltraFast 设计方法;时序约束不良;过高资源利用率;控制集过多;未采用最优化时钟设置;逻辑层次过多,难以达成目标性能;布局规划不良;布线拥塞;因约束导致工具优化受限。

前一篇文章《Python 中如何实现参数化测试?》中,我提到了在 Python 中实现参数化测试的几个库,并留下一个问题:它们是如何做到把一个方法变成多个方法,并且将每个方法与相应的参数绑定起来的呢?我们再提炼一下,原问题等于是:在一个类中,如何使用装饰器把一个类方法变成多个类方法(或者产生类似的效果)?

随着USB接口的越来越普及,现在几乎所有的接口都可以转换成USB接口,本文主要介绍一下Xilinx FPGA的JTAG接口转换成USB接口的方案。

Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法,还是从对使用者思路的要求,都是全新的;在运行速度、算法优化和功能整合等很多方面都有了显著地改进。

AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。