逻辑电平之差分互连(6-1)

judy 在 周四, 12/06/2018 - 16:56 提交

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

下面详细介绍第一部分:同种逻辑电平之间的互连。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

下面详细介绍第一部分:同种逻辑电平之间的互连。

CANopen是一种架构在控制局域网路(Controller Area Network, CAN)上的高层通讯协定,包括通讯子协定及设备子协定常在嵌入式系统中使用,也是工业控制常用到的一种现场总线。CANopen 实现了OSI模型中的网络层以上(包括网络层)的协定。CANopen 标准包括寻址方案、数个小的通讯子协定及由设备子协定所定义的应用层。

作者:Mculover666

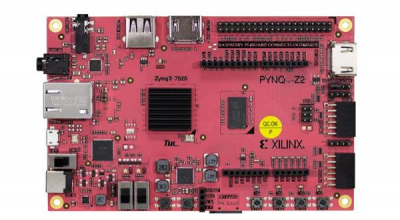

今天刚刚到手一块PYNQ-Z2,确认过眼神,是我想要的板子,话不多说,开干。

在goggle上搜zcu102 pynq可以找到一些移植方法的信息

0. Prebuilt

PYNQ移植ZCU102编译好的固件

上一节我们观察了AXI总线的信号,了解了基于AXI总线读写的时序,这一节我们继续探索基于AXI总线的设计,来看一看ZYNQ系列开发板的独特优势,PS可以控制PL产生定制化的行为,而不需要去动硬件代码。

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

首先打开vivado2017.3新建一个RTL项目。

点击Flow navigator的IP Catalog 选项,如下图所示:

一. 概述

Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

在用Vivado建立工程的时候选择器件的时候就可以看到这些资源的多少。如下图所示。

本篇主要介绍TTL/CMOS电平的互连、OC/OD的互连,其余单端逻辑电平的互连可参考相关器件规范、电平规范。

1、TTL/CMOS互连

本培训视频介绍了 AWS F1 硬件平台的技术规格。观看此视频,以了解 AWS FPGA 中的各个区域,了解AWS F1 Shell 并查看重要的性能注意事项。

QNX版本:QNX6.6

宿主系统:Windows

交互系统:Debin

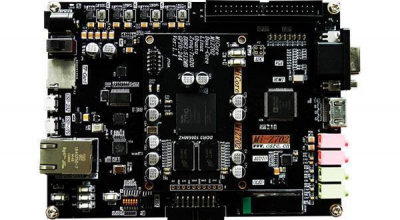

开发板:MIZ702 完全兼容ZedBoard