xilinx zynq RapidIO系统配置

judy 在 周一, 11/12/2018 - 16:03 提交

参考

书籍《RapidIO The Embedded System Interconnect》

xilinx手册pg007《Serial RapidIO Gen2 Endpoint v4.1 LogiCORE IP Product Guide》

Zynq-Linux移植学习笔记之14-RapidIO驱动开发

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

参考

书籍《RapidIO The Embedded System Interconnect》

xilinx手册pg007《Serial RapidIO Gen2 Endpoint v4.1 LogiCORE IP Product Guide》

Zynq-Linux移植学习笔记之14-RapidIO驱动开发

这年头GitHub可谓是程序员必备交友技能。毫无疑问GitHub现在已经是全球最大的开源社区了,也常常被人戏称为“全球最大同性交友平台”。

你可以在这里follow各种开源社区的技术大牛,学习到各种各样的开源技术和开源项目。

那么作为一个嵌入式工程师,我们应该如何用好GitHub呢?GitHub可以用来做些什么好玩有意思的事情呢?

分号

Tip

不要在行尾加分号, 也不要用分号将两条命令放在同一行。

行长度

Tip

每行不超过80个字符

例外:

1. 长的导入模块语句

2. 注释里的URL

不要使用反斜杠连接行。

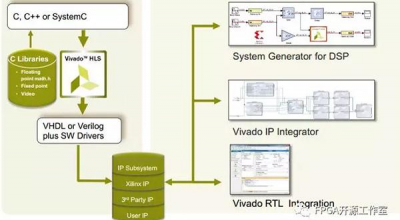

DA(Vivado)软件可以很好的帮助我们更好的去学习FPGA相关知识,例如:

作者:Matt Chevrier,德州仪器

为工业以太网器件供电需要解决工业以太网和工业应用的几个特定问题。

标准以太网与工业以太网之间最大的区别在于拓扑结构,如图1所示。标准以太网为星形拓扑,而工业以太网则包含线形、树形和环形等多种不同的拓扑结构。

作者:Huster-ty

前言:

ZYNQ 7000有三种GPIO:MIO,EMIO,AXI_GPIO

MIO是固定管脚的,属于PS,使用时不消耗PL资源;EMIO通过PL扩展,使用时需要分配管脚,使用时消耗PL管脚资源;AXI_GPIO是封装好的IP核,PS通过M_AXI_GPIO接口控制PL部分实现IO,使用时消耗管脚资源和逻辑资源。

为了快速实现算法板级验证,PC端需要通过JTAG或以太网与FPGA形成通路。最简单便捷的方案是利用协议栈芯片,用户可以无视底层,利用简单的SPI协议读写寄存器实现复杂的TCP UDP等网络协议。当然带宽会受限于SPI接口有效速率,本文采用芯片为W5500,支持10M/100M自适应,其理论值高达80Mbps,基本达到算法验证的要求。

作者: OpenSLee,来源:FPGA开源工作室

1. 背景知识

在Xilinx提供的很多ip如VDMA ,OSD,Mixer,TPG等等,在使用前都需要进行配置,配置接口往往是AXI-Lite接口,正常情况下我们一般自己编写配置逻辑或者通过MB/ZYNQ等对IP进行配置,如果在我们使用到XDMA的同时也使用到需要AXI-Lite配置的ip的话,那么有一种新的方法可以对这类型IP进行配置。