Vivado时序分析练习

judy 在 周五, 10/19/2018 - 09:10 提交

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。

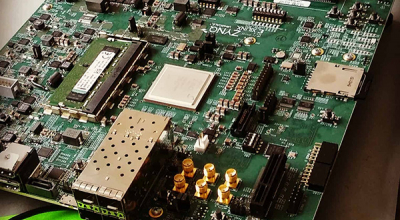

这次的练习选择的是ZYNQ的芯片,原本工程是工作在100MHz的时钟,但是作为练习,我们可以把时钟调到一个极限的程度来进行优化。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。

这次的练习选择的是ZYNQ的芯片,原本工程是工作在100MHz的时钟,但是作为练习,我们可以把时钟调到一个极限的程度来进行优化。

tftp

可传输单个文件,不能传文件夹

需要通过命令传输文件,略显复杂

==一般调试kernel时,用uboot通过tftp方式启动,不用每次都烧写存储介质==

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。

源代码级别调试

Vivado Simulator提供了在仿真过程中debug设计的特性,通过为源代码添加一些可控制的执行条件来检查出问题的地方。总的来说有三种调试方法:

本博文主要是对基于PCIE(mcap)的部分可重构实现的步骤做一个简单的演示,如有错误之处,欢迎批评指正。值得说明的是,基于PCIE的部分可重构需在ultrascale系列及ultrascale+芯片才能实现,具体哪些系列能实现哪种配置方式如下图所示:

有了BOOT.BIN(fsbl+pmu+atl+uboot)、uImage、uramdisk.image.gz,dtb文件,就可以启动了。把上述文件统统拷贝到SD卡,并设置开发板为SD卡启动。

本文是该系列的第22篇。上一篇介绍了使用Image From File和Video Viewer完成图像的采集和输出,并将两部分分别打包为子系统,使其具有通用性。本文将介绍如何使用Simulink提供的回调函数机制,实现从MATLAB工作空间采集和输出图像。

开发环境:

Windows下的Vivado套件

Linux ubuntu

PYNQ = Python + ZYNQ —— ZYNQ部分功能的Python化

PYNQ

优点:

1、 Python用于ZYNQ开发,Python库和FPGA硬件库可以直接调用,极大加快开发进程、缩短开发周期、降低开发难度,更方便、快捷;

在设计中,所有的算数运算符都是按照无符号数进行的。如果要完成有符号数计算,对于加、减操作通过补码处理即可用无符号加法完成。对于乘法操作,无符号数直接采用“*”运算符,有符号数运算可通过定义输出为 signed 来处理。