Vivado常见问题集锦

judy 在 周五, 08/10/2018 - 16:43 提交

作者:NingHeChuan(宁河川)

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

作者:NingHeChuan(宁河川)

简介

本篇博客大部分内容前三篇博客都已经包含了,此处重点叙述不同之处,主要对比Tcl命令的不同和解决SDSoc程序找不到基地址的问题。

使用ZedBoard开发板,SDSoc 2017.4, Win10系统;此处通过AXI_GPIO点亮ZedBoard板子上连接在PL端的8个LED灯。

作者 | Conor Dewey

编译 | 专知

整理 | Yingying, Jiahui

本文是该系列的第9篇。FPGA设计中经常用到一些控制逻辑,如有限状态机(FSM),如果用各种block搭建一个FSM比较麻烦。System Generator支持调用MATLAB代码,通常可以编写MATLAB代码来实现FSM等控制逻辑,通过MCode block调用到System Generator设计中。

近日,想必各位科技爱好者的朋友圈都被一篇发表在第25届IEEE国际讨论会上,用Python开发FPGA的论文刷屏了吧,那么这是如何实现的呢?今天,就请各位看官和小编一起来了解一下,这个构想的实现基础——PYNQ。

作者:Paul S.Levy, 赛灵思功能安全系统高级工程师

简介

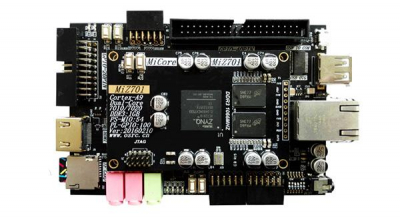

前段时间买了一块米联客的7010开发板,打算尝试为这块开发板搭建一个简单平台。

用户自定义开发板与SDSoc直接支持的开发板的区别在于,直接支持的开发板已经根据板子上的硬件完成了一系列重要配置(如时钟、DDR型号),所以在为用户开发板搭建平台时,只需要根据该开发板的硬件实际情况进行相应的配置即可。

1.定义

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

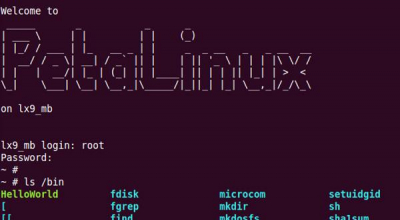

前言

PetaLinux 工具提供在 Xilinx 处理系统上定制、构建和调配嵌入式 Linux 解决方案所需的所有组件。理想适用于提升设计生产力,该解决方案与 Xilinx 硬件设计工具协同工作,为 Zynq® UltraScale+™ MPSoC、 Zynq®-7000 SoC、和 MicroBlaze™ 简化了 Linux 系统的开发。