充分发挥 Python 的威力:用最简单的方法打造互联互通的智能产品

judy 在 周四, 08/02/2018 - 10:47 提交

作者:赛灵思工业物联网战略部 Chetan Khona

智能互联产品背后的心理学

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

作者:赛灵思工业物联网战略部 Chetan Khona

智能互联产品背后的心理学

1. Matlab中数组元素引用有三种方法:

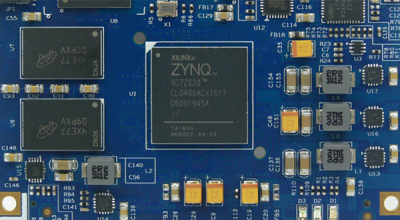

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。

涉及到AXI BRAM Controller 和 Block Memery Generator等IP的使用。

一、梯度下降法

在机器学习算法中,对于很多监督学习模型,需要对原始的模型构建损失函数l,接下来便是通过优化算法对损失函数l进行优化,以便寻找到最优的参数θ。在求解机器学习参数θ的优化算法中,使用较多的是基于梯度下降的优化算法(Gradient Descent, GD)。

本文是该系列的第6篇。第2篇中以数字滤波器的设计为主题,介绍了System Generator的完整设计流程;第4篇对设计进行了资源分析。本文将在此基础上,讨论如何对设计进行优化,以及介绍System Generator可以导入MATLAB的工作区(workspace)变量的特性。

ADC

ADC是模数转换器转换器 的供应商的英文简称,是一种能将模拟信号转变为数字信号的电子元件。通常是将信号采样并保持以后,再进行量化和编码,这两个过程是在转化的同时实现的。

作者:张凤麒,张延彬,王忠勇;2018年电子技术应用第7期

摩尔定律失灵了,已是不争的事实。单纯的提升一种芯片性能变的代价越来越高,与此同时,异构计算成为提高计算力的主流方向。

什么是异构计算?

异构计算的前景怎么样?

OpenPOWER系统上FPGA异构计算的先进技术又有哪些?

本文是该系列的第3篇,上一篇以数字滤波器的设计为主题,介绍了System Generator的完整设计流程,最后自己编写testbench在示例工程中对System Generator导出的IP核进行测试。其实System Generator就可以导出整个设计的说明文档以及一个testbench,本文将介绍如何使用该特性。

很多人拿到uboot,编译不知如何下手!

其实,这个世界上的万事万物,都有一个“纹理”。庖丁解牛之所以游刃有余,是因为他掌握了牛的纹理,顺着这些纹理就应该很容易。

那么我们的uboot的纹理在哪里呢?