YunSDR通信小课堂(第32讲)

judy 在 周四, 04/03/2025 - 16:25 提交

即使最好的数据转换器中也存在噪声和杂散,因此必须采用策略来减轻它们的影响,如频率规划。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

即使最好的数据转换器中也存在噪声和杂散,因此必须采用策略来减轻它们的影响,如频率规划。

如今,边缘采集的数据量十分庞大。据 Gartner 预测,到 2025 年,将有多达 75% 的企业数据会在传统数据中心以外生成

本例程采用基于SPI Master和BPI Master接口的远程升级方案,在远程升级的过程中,用户通过通信协议或专用接口从远端接收位流

DR1 FPSoC®系列集成了高性能硬核处理器、足量的高速片上内存、丰富的外设接口、FPGA 可编程逻辑单元以及NPU/JPU等硬件加速引擎

本文将详细分析这些步骤中的优化挑战,并提出一些可能的解决方案,以帮助设计者在保证仿真性能的同时,最大限度地减少编译时间。

在 24.2 版本中,GT Wizard 迎来了重要的更新,添加了新的IP: GT Wizard 子系统。旨在为用户带来更高的灵活性和兼容性。本博客将介绍 GT Wizard 子系统的使用方式。

SerDes的实现包括并行到串行(串行到并行)数据转换、阻抗匹配电路和时钟数据恢复功能。SerDes的主要作用是尽量减少I/O互连的数量。

本文将为大家详细介绍在 Linux 系统中通过预留物理内存实现 ARM 与 FPGA 高效通信的方法

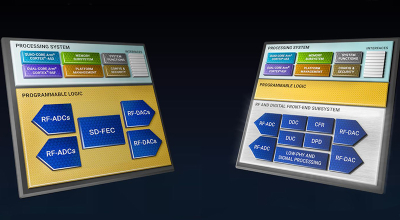

AMD Xilinx的RFDC驱动API提供了高度灵活的配置能力,涵盖混频器、QMC、时钟同步等关键功能,支持动态更新与多设备同步

功能上,RF-DAC内的复混频器与RF-ADC内的混频器相同;不同之处在于它在RF-DAC中的作用是调制数据,而不是解调数据