必看!基于ARM+FPGA SoC国产平台的B码对时,破解电力授时难题

judy 在 周三, 01/22/2025 - 11:09 提交

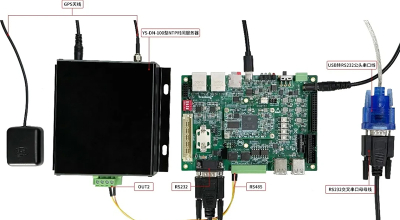

今天分享一个基于复旦微FMQL20S400M四核ARM Cortex-A7(PS端)+FPGA可编程逻辑资源(PL端)异构多核SoC处理器的B码对时案例,开发环境如下

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

今天分享一个基于复旦微FMQL20S400M四核ARM Cortex-A7(PS端)+FPGA可编程逻辑资源(PL端)异构多核SoC处理器的B码对时案例,开发环境如下

前面我们介绍了IP核配置和调用的相关注意事项,现在我们基于Zynq7020实际上板看看调试的一些细节。

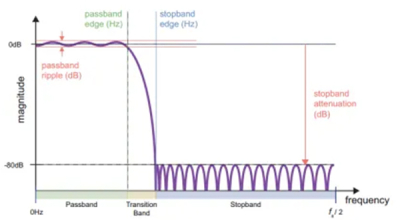

在时域信号处理的世界里,将信号分解成正弦波的和一直是前进的方向。原因很简单。如果一个正弦波被输入到一个线性系统,那么输出就是一个完全相同频率的正弦波

小型FPGA广泛应用于各种设备、应用和行业,因为它们能够可靠地执行对许多不同类型智能系统的快速运行至关重要的关键功能

AIE graph通过PLIO与PL(programable logic)连接, 以交换数据, PLIO既可以通过DMA S2MM或者MM2S连接到AI Engine的buffer

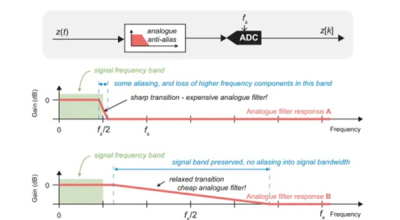

如前所述,可以通过对信号进行采样和量化来将连续时间模拟信号转换为数字等效信号,与这些操作相关的关键参数是采样率和量化器中使用的量化位数。

本文主要从应用的角度出发,介绍一下,如何使用SEM IP。

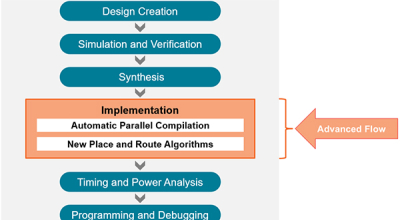

本文介绍了 Versal 的Advanced Flow,这是 Vivado 2024.2 版本提供的一套新的布局布线功能。

从时域到频域的转换的简单描述如图3.14所示。离散傅里叶变换(DFT)通常以更有效的形式实现为快速傅里叶变换(FFT)

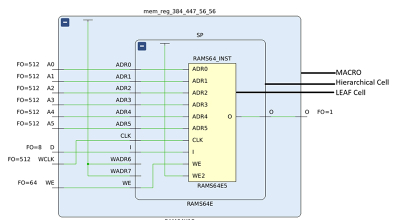

几乎所有 AMD 可编程器件都具有 CLB 资源,可以在 LUT 中实现小型存储器。在网表中,这些资源被称为 LUTRAM 或分布式 RAM。