CPM PCIE做RC时如何完成对复位信号的控制

judy 在 周五, 11/29/2024 - 16:55 提交

本篇文章通过举例来说明,用户如何根据自己的硬件电路设计来实现对EP端复位的控制

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本篇文章通过举例来说明,用户如何根据自己的硬件电路设计来实现对EP端复位的控制

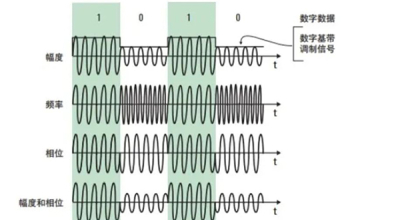

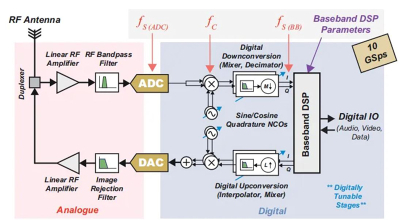

接收机从本质上说是发射机的反向实现,但在设计上更为复杂。接收机首先把输入的射频信号下变频为中频信号,然后进行解调

环回(loopback)是GT的一种特殊配置模式。可以把发送端的数据直通过自身PMA层或对方器件(不加进一步处理)后再转回给发送器件的接收端

这样在频率a载波下产生了双边带信号:a+b和a-b,而对于信号传输来说,其实只需要一个信号即可。

本文讨论中你将进一步了解I和Q分量,以及数字系统使用它们的原因。

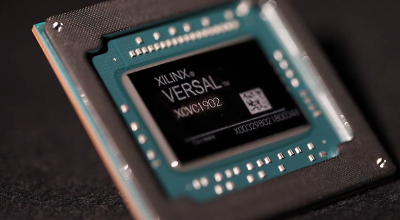

Versal CPM QDMA EP Design 默认状态下的Setup Debug流程及debug core 时钟,以Vivado 2024.1为例

SGMII在现代网络基础设施中发挥着重要作用,它不仅能促进网络设备之间的高速通信,还能灵活兼容各种物理层技术

本文讲解一下如何通过HqFpga软件生成可调用的网表文件以及ballmap功能的使用

今天简要介绍实现无线电系统调制和解调的主要方法,这在软件定义无线电(SDR)的背景下很重要。

我们在Versal上开发驱动程序的时候,经常会访问某些硬件寄存器,读取或者写入某个值