【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十四章 PS端SD卡读写

judy 在 周五, 01/29/2021 - 09:36 提交

本章介绍使用FatFs文件系统模块读取SD卡的BMP图片,并通过DP显示。

本章介绍使用FatFs文件系统模块读取SD卡的BMP图片,并通过DP显示。

本章介绍PS端DisplayPort的使用。Vivado工程仍然基于“ps_hello”

PS端I2C的使用

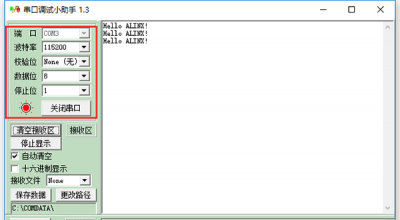

在前面的实验中,大家或多或少会发现有打印信息的情况,主要是调用”xil_printf”或”printf”,但是通过什么打印信息呢?我们还记得打印信息之前设置了串口,是的,确实是串口,但这些函数是如何调用串口呢?其实我们可以在”xil_printf”函数定义中看到,注意outbyte函数就是调用UART打印的

实时时钟(rtc)单元为系统和应用软件提供精确的时间基准。为了满足高精度的需要,实时时钟还包括校准电路,以补偿温度和电压波动。RTC 由 VCC-PSAUX 或 VCC-PSBATT 电源供电。当辅助电源可用时,RTC 使用它保持计数器活动。当辅助电源不可用时,RTC 自动切换到 VCC PSBATT 电源。

此文基于第十八章内容进行软件开发

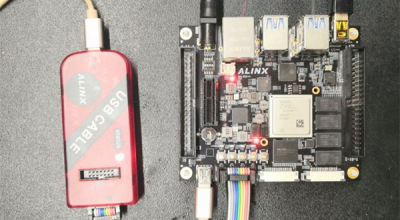

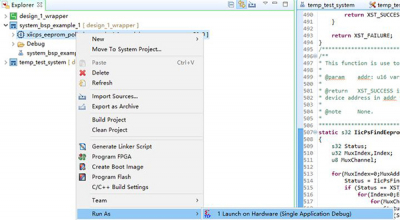

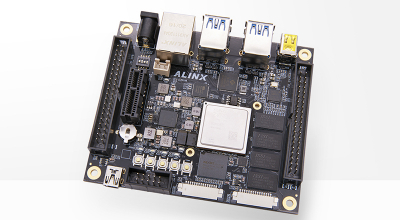

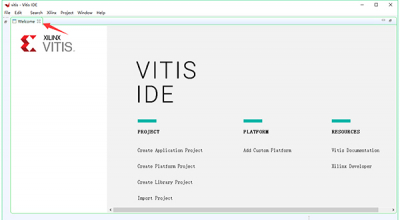

前面的实验都是在PL端进行的,可以看到和普通FPGA开发流程没有任何区别,ZYNQ的主要优势就是FPGA和ARM的合理结合,这对开发人员提出了更高的要求。从本章开始,我们开始使用ARM,也就是我们说的PS,本章我们使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性。

所有的工程目录下都有个bootimage文件夹,存放了对应的BOOT.bin文件,可将此文件拷贝到Vitis_image_download文件夹,覆盖原有的BOOT.bin。也可以把BOOT.bin放到SD卡启动验证功能

基于HDMI输出实验,本章介绍7寸液晶屏的显示。LCD屏显示方式从屏幕左上角一点开始,从左向右逐点显示,每显示完一行,再回到屏幕的左边下一行的起始位置,在这期间,需要对行进行消隐,每行结束时,用行同步信号进行同步

在HDMI输出实验中讲解了HDMI显示原理和显示方式,本实验介绍如何使用FPGA实现字符显示,通过这个实验更加深入的了解HDMI的显示方式。