瑞苏盈科双Andromeda XRU50 RFSoC模块架构:构建先进实时频谱监测解决方案

judy 在 周五, 05/23/2025 - 09:58 提交

瑞苏盈科推出的基于双Andromeda XRU50 RFSoC模块架构的实时频谱监测解决方案,以 “双芯协同” 为核心,实现了从信号采集到分析的全链路技术突破

瑞苏盈科推出的基于双Andromeda XRU50 RFSoC模块架构的实时频谱监测解决方案,以 “双芯协同” 为核心,实现了从信号采集到分析的全链路技术突破

本篇博文主要涵盖了 AMD 为集成的 RF Data Converter 提供的公共资源。

当使用RFSoC进行原型设计时,通常需要外部无线电组件。例如,可能需要天线来改善信号采集,或者需要外部滤波器来抑制频谱混叠

通过重新检查先前考虑的Vivado工作流,可以突出强调协同设计方法。图11.10说明了Vivado和Vitis生态系统中的这种集成设计方法

在设计RFSoC PS时,必须选择合适的软件堆栈来满足设计要求。软件栈是一组基本软件,开发人员可以在这些软件的基础上添加他们自己的定制软件

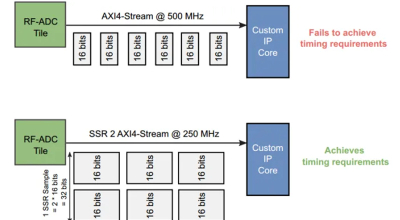

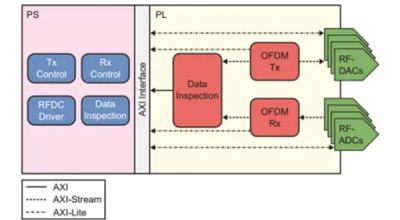

RFSoC器件分为两个主要的可定制部分,处理系统(PS)和可编程逻辑(PL)。在为RFSoC设计系统时,值得首先考虑的是设计的功能如何在这两个元素之间进行划分

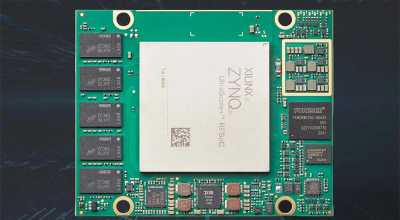

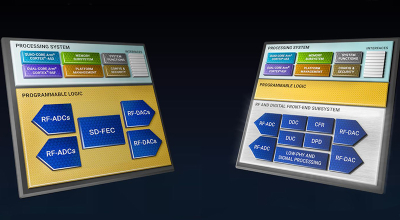

Andromeda XRU50 RFSoC具有无与伦比的灵活性,是下一代无线和卫星通信系统、测试和测量设备甚至量子计算等各种嵌入式应用的理想之选。

AMD Xilinx的RFDC驱动API提供了高度灵活的配置能力,涵盖混频器、QMC、时钟同步等关键功能,支持动态更新与多设备同步

基于AMD Zynq UltraScale+™ RFSoC Gen3 XCZU49DR 芯片的 16 通道 14 位 2.5GSPS ADC 与 16 通道 14 位 9.85GSPS DAC,实现全数字域直接射频采样

RFDC这个IP,是RFSoC系列中ADC、DAC的核心。这个IP和PL的资源有互联通道,和ARM相对是独立的。