课时4:Vitis HLS中数据类型定义——Vitis HLS教程

judy 在 周二, 05/17/2022 - 15:24 提交

采用任意精度数据类型,可以在获得相同精度的运算条件下,运算速度更快且使用更少的资源。

采用任意精度数据类型,可以在获得相同精度的运算条件下,运算速度更快且使用更少的资源。

本文我们通过一个具体的实例,演示HLS设计流程。

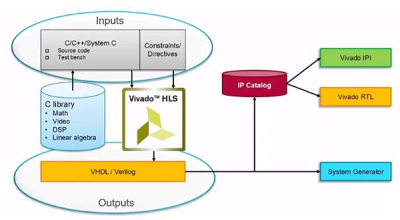

传统的FPGA RTL设计流程主要是采用VHDL、VerilogHDL或System Verilog进行工程的开发,同时也是通过硬件描述语言来编写测试案例对开发的工程进行仿真验证

Vitis HLS是一个高级综合工具。用户可以通过该工具直接将C、 C++编写的函数翻译成HDL硬件描述语言,最终再映射成FPGA内部的LUT、DSP资源以及RAM资源等。

请问下截图所示的是不是指内核所需要使用的硬件资源比例? 遇到下面的报错时,该如何排查和避免问题呢?

vitis_hls 命令默认以 GUI 模式打开。要查看哪些选项可用于vitis_hls,可以使用-help选项

为什么Vitis HLS中的浮点累加器的精度与IEEE单精度浮点累加器不同?

Vitis HLS 对 C 语言的支持与 Vivado HLS 工具不同。本文描述了Vitis HLS工具的C语言支持能力。

Vitis HLS 的 2021.1 GUI 中添加了许多新功能。请参阅下面的详细信息。

本部分通过将 HLS IP 和 Testbench 设计发送给编译器进行编译和执行,来执行 HLS 流的 C仿真阶段。