延时开始SEM功能的扫描(二)

judy 在 周二, 03/12/2024 - 15:05 提交

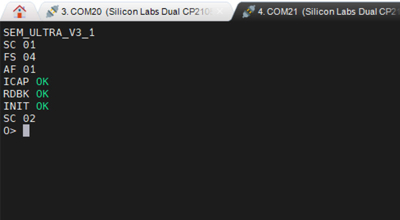

本文介绍如何推迟XilSEM扫描功能的开始。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本文介绍如何推迟XilSEM扫描功能的开始。

Versal 包含了 Cortex-A72 处理器和 Cortex-R5 处理器,PL 端可编程逻辑部分

Vitis Unified IDE使用“System Device Tree (SDT)”将硬件元数据从Vivado传递到 Vitis

每个工程下面都有一个生成vivado的脚本,用于重建vivado工程

在 2023.2 版的全新 Vitis Unified IDE 中,不再生成 DeviceID 作为索引参数用于独立 BSP 驱动程序内的

了解该系列器件如何帮助设计人员以低成本推动 I/O 密集型应用产品快速上市

本文详细描述了 UNIMACRO 库。

本文介绍如何在Versal器件中推迟XilSEM的扫描工作

如果设计必须采用分立式PHY,那么在选择PHY时应牢记几个标准

本文介绍多种方法供您用于判断评估板上的器件是工程样品 (ES) 还是量产芯片