在MPSoC器件中使能SEM IP (一)

judy 在 周五, 03/01/2024 - 11:48 提交

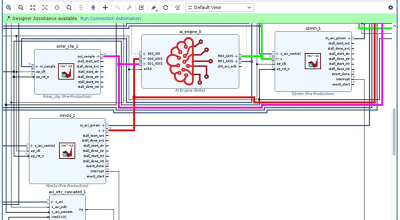

SEM IP的主要任务就是扫描PL Configuration RAM, IP自身也是运行在PL里面的

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

SEM IP的主要任务就是扫描PL Configuration RAM, IP自身也是运行在PL里面的

本文介绍FPGA工程师在进行ISP设计时需要考虑的一些关键点

当 Versal GTY/GTYP 的掉电端口断言有效时,时钟和输入/输出数据的预期行为是什么?

本文讲解如何使用 AIE API 进行 AI 引擎内核代码矢量化

采用相同工具输入的情况下,Vivado 结果是否可重复?

在文中,我们将构建系统、分析生成的输出并在硬件仿真中使用 QEMU 运行系统。

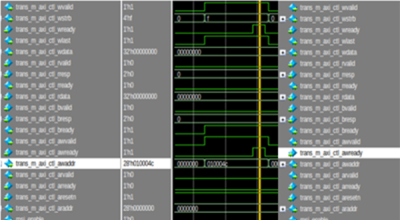

本文将介绍一种可适用于上述场景的方法,即在下载 Bitstream 后自动触发 ILA 采集,为硬件调试提供更多便利。

Xilinx PCIE IP中MSI中断相关的地址如下图1所示

System Generator是AMD一款系统级建模工具,有助于加快FPGA的硬件设计

本文继续探讨微控制器到现场可编程门阵列接口。