如何在Vivado中用工程模式使用DFX流程

judy 在 周二, 04/23/2024 - 15:33 提交

本文介绍在Vivado中用工程模式使用DFX流程以及需要注意的地方。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本文介绍在Vivado中用工程模式使用DFX流程以及需要注意的地方。

使用IBERT测试误码率和眼图必须有个收发环通的硬件,开发板上有2个SFP光纤接口,本实验把2个光接口收发两两连接,形成2个收发环通链路。

通过将数据管理堆栈与英特尔 FPGA 和开放式 FPGA 堆栈 (OFS) 相结合,SigmaX 显著提高了生成数据的效率

在使用DFX流程时,有用户希望在完成初始Configuration的Implementation之后,能加速后续RM的实现过程

关于如何在FPGA中实现TCAM功能有不少的论文,在翻阅借鉴之后,本文就TCAM在FPGA上的最优化实现进行探讨。

尽管这两种标准长期以来一直用于串行通信,但 RS-485 提供了 RS-232 所不具备的宝贵功能。在本文中了解更多信息。

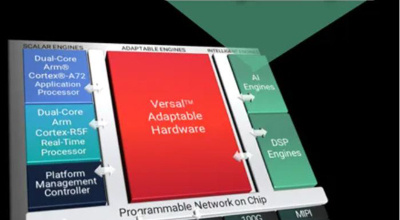

有很多文档都描述了AI Engine的架构和性能参数,但是看完这些后,现实中遇到的问题最多的是这个AI Engine到底怎么用

系统看门狗定时器(System WatchDog Timer)通常用于嵌入式系统,可以有效的防止软件错误、系统死锁、篡改以及意外行为

在FPGA中,动态相位调整(DPA)主要实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。

实验Vivado工程为“lvds_lcd”。本章介绍lvds lcd液晶屏的color bar显示。