Napatech IPU解决方案助力优化数据中心存储工作负载

judy 在 周一, 05/13/2024 - 16:54 提交

这篇解决方案简介介绍了Napatech的集成式软硬件解决方案如何将存储工作负载从主机CPU卸载到IPU,同时在应用级别保持完整的软件兼容性。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

这篇解决方案简介介绍了Napatech的集成式软硬件解决方案如何将存储工作负载从主机CPU卸载到IPU,同时在应用级别保持完整的软件兼容性。

此教程介绍一种通过双通道DMA,采用PingPong传输的方式,以提高实时数据的处理能力,减小对硬件资源的依赖。

本文可让开发者们看懂 AMD Vivado™ Design Tool 2023.2 中的“AMD Versal™ Adaptive SoC CPM PCIE PIO EP 设计”CED 示例。

AMD 提供了支持不同速度的多种以太网 IP。此外,还提供了设计示例供用户用作参考。请参阅以下以太网设计示例列表。

本参考设计基于ZYNQ开发板, 使用VDMA做原始图像采集系统,在petalinux下做服务器,通过Socket发送图像至Windows或者Linux上位机。

开发板有两路千兆以太网,通过RGMII接口连接,本实验演示如何使用Vitis自带的LWIP模板进行PS端千兆以太网TCP通信。

本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使用的是 Vitis Unified IDE。

本文将会详细介绍关于DPU Fingerprint的相关内容,并提供此类校验失败问题的检查手段和解决方案。

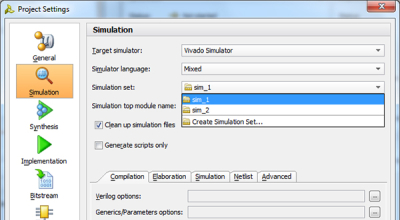

Vivado 具有一个功能特性,能够将这些文件便利地排列组合为多个可轻松访问的不同仿真集。本文描述了如何在 Vivado 中使用多个仿真集。

本文主要讨论一下如何在外部数据文件中指定RAM 初始内容。