FPGA时序约束实战篇之多周期路径约束

demi 在 周一, 02/10/2020 - 14:33 提交

多周期路径,我们一般按照4个步骤来约束:有使能的数据;两个有数据交互的时钟之间存在相位差;存在快时钟到慢时钟的路径;存在慢时钟到快时钟的路径。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

多周期路径,我们一般按照4个步骤来约束:有使能的数据;两个有数据交互的时钟之间存在相位差;存在快时钟到慢时钟的路径;存在慢时钟到快时钟的路径。

本文主要介绍Zynq UltraScale+ MPSoC系列器件的PS-PL之间互连的AXI总线接口。

创建 FPGA 设计和维护 Vivado® 设计套件项目时,版本控制系统对于团队合作可能是一项具有挑战性的任务。工程师必须能跟踪设计变更,完整地从 HDL 或 TCL 源代码再现项目并交付特定的项目状态。

在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径。

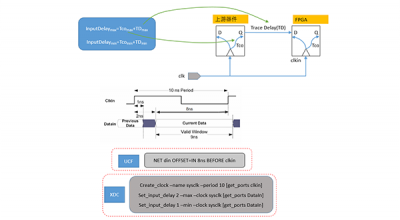

I/O约束是必须要用的约束,又包括管脚约束和延迟约束。管脚约束就是指管脚分配,我们要指定管脚的PACKAGE_PIN和IOSTANDARD两个属性的值,前者指定了管脚的位置,后者指定了管脚对应的电平标准。

十多年前,我们不会料到加速器在数据中心会这么流行。尽管它们并不普遍,但许多新的工作负载具备加速条件,并且移植工作使旧版应用程序可以卸载以提高性能。这种过渡在GPU上最为明显,但人们寄希望于FPGA将继续发展。

下一代基因组测序(Next Generation Sequencing ,NGS)是一个很有意义的工作,全球很多国家都在积极的参与这件事情。这需要多个学科的结合,不仅仅是生命科学,计算机科学的软件和硬件都可以在这个人类的大工程中发挥强大的力量。

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

跳频通信具有良好的抗干扰、抗多径衰落、抗截获等能力和同步迅速等特点,广泛应用于军事、交通、商业等各个领域。其关键技术主要有三点:跳频序列发生器、跳频频率合成器和跳频同步器。

① 滤波电容的放置要与电源接近,振荡器也是,在振荡器前端放电阻。② 通过Design的Board Shape改变电路板大小。