在 FPGA 上快速构建 PID 算法

judy 在 周一, 10/31/2022 - 12:05 提交

作为一名工程师,在项目实施阶段多多少少会遇到需要使用控制理论的应用程序。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

作为一名工程师,在项目实施阶段多多少少会遇到需要使用控制理论的应用程序。

让我们从触发器开始,所有触发器都有一个围绕活动时钟沿的建立(setup time)和保持窗口(hold time)

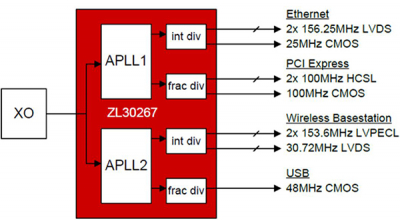

随着FPGA的功能越来越强大,并且有SOC等异构的架构不断演进,硬件设计也有更多的时钟要求

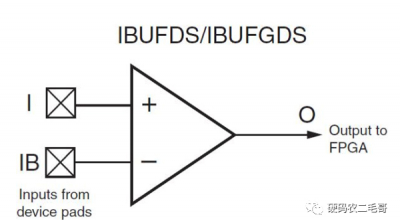

FPGA开发中经常会用到LVDS信号,本文分别介绍intel fpga和xilinx fpga的LVDS信号处理方法。

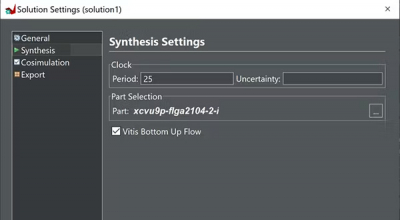

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

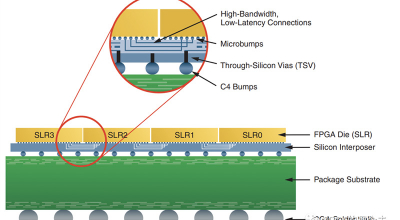

大家使用xilinx的多die FPGA时,或多或少的都遇到过时序收敛问题,那么对于多die的FPGA我们应该如何做好设计了。

最近看到很多人问FPGA如何入门,或者如何学习的问题,突然想起自己刚工作的时候,部门的培养还是做的很不错的

用FPGA来做硬件加速,也有十年的时间了,最近我在回顾这些年的项目经历时,突然有了一个想法

自适应计算,这一创新理念可以给行业带来什么?加入AMD之后,赛灵思(Xilinx)给出了更丰富的答案。