【Vivado那些事儿】XilinxCEDStore介绍

judy 在 周三, 06/22/2022 - 09:36 提交

之前很多人问我有没有好的代码可以参考,我之前一直推荐的是官方的IP参考例程/IP源码,但是不知道大家有没有看过官方的项目例程,看下下图

之前很多人问我有没有好的代码可以参考,我之前一直推荐的是官方的IP参考例程/IP源码,但是不知道大家有没有看过官方的项目例程,看下下图

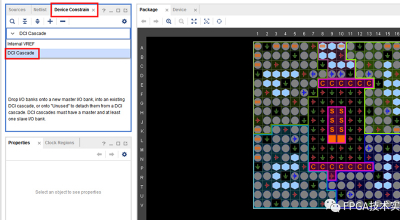

Vivado®Design Suite提供了几种可能影响I/O和时钟规划的器件规划功能。例如,FPGA配置方案、约束、配置电压方式都会影响I/O和时钟规划。

在Vivado里,可以从Block Design导出TCL脚本,保存工程。之后可以从TCL脚本恢复工程。导出的TCL脚本中,可能不包含用户IP的路径信息

report_clock_interaction矩形框内的不同颜色表征了不同时钟域之间的路径所呈现的约束状态而非Slack(时序裕量)的恶化程度

在VCS中,一个仿真会话可以保存在一个Tcl文件中,以后可以加载。当我从Vivado调用VCS时,如何加载一个保存的会话?

我在一个自定义平台上运行我的项目,而我的目标平台的Vivado项目在Vivado合成中使用了以下额外选项。当我运行Vitis链接器时,我看到以下错误。

本人业余搞FPGA开发的同时,还喜欢研究生产力工具,包括硬件和软件的,电脑就是重中之重,恰好今年手中有个还算比较大FPGA工程,综合一次相当费时,索性把以前记录的

在Vivado或其他综合工具(如Synplify)上,综合阶段需要添加什么约束呢?

在本文中,我们以vivado自带综合器为例、以verilog为编程语言,看看如何理解和利用警告信息排除代码中的小bug。

使用DSP的方法一般有两种:让综合器自己推断、例化DSP原语。有的时候为了偷懒或者有的计数器之类的需要跑高速,则可以让计数器也使用DSP实现。