AXI EPC IP 使用详细说明

joycha 在 周五, 09/23/2022 - 09:51 提交

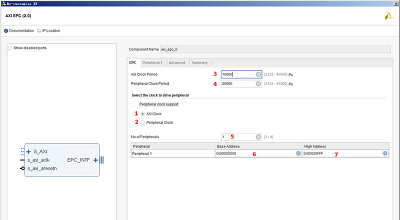

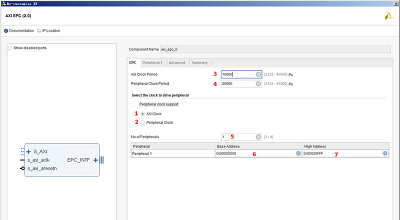

Xilinx FPGA 内嵌的 CPU ,可以通过 AXI EPC 在 FPGA 芯片外接多个多种外设芯片

Xilinx FPGA 内嵌的 CPU ,可以通过 AXI EPC 在 FPGA 芯片外接多个多种外设芯片

在本实践中,我们将实际实现 HLS 组件作为 FPGA 设计的一部分

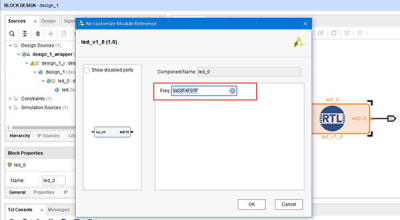

用Vivado开发ZYNQ时,常用到Block Design。Block Design中不仅仅可以添加IP核

在对工程进行综合时,出现综合过程中出现中止或者完全不启动综合,类似下图,明明点击综合启动了几分钟

在异步跨时钟域场合,对于控制信号(通常位宽为1bit)常使用双触发器的方式完成跨时钟域操作

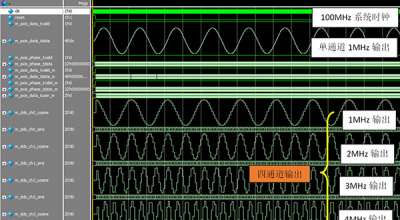

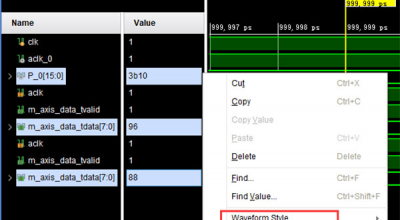

本文我们通过例化Xilinx公司的DDS IP核来产生混频器本振输入频率,并给出Modelsim仿真测试结果。

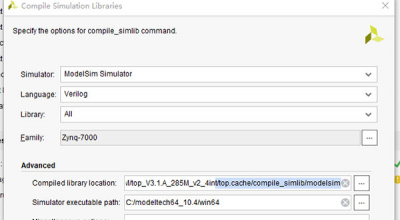

如果只是纯的.v文件仿真那很容易操作,主要是涉及到IP核,那么就必须要对vivado的IP核的库文件进行编译

本实验要完成利用vivado中的DDS IP核对两个正弦波进行混频,实现数字下变频或者上变频。

Vivado 中的 sigasi 功能特性使用高速缓存,有时高速缓存大小可能高达数百 MB,导致主目录中存储器减少,从而影响 Vivado 性能。

在设计代码的时候,大部分人都是习惯于使用外部的编辑器进行设计,而不是使用vivado自带的编辑器