2022.2(和更低)版本的 Vivado:Versal XPIO IOLOGIC 可能将捕获时钟反相

judy 在 周二, 02/14/2023 - 17:18 提交

Versal XPIO IOLOGIC 包含 IDDR、IFD、IDELAY、ODDR、OFD 和 ODELAY

Versal XPIO IOLOGIC 包含 IDDR、IFD、IDELAY、ODDR、OFD 和 ODELAY

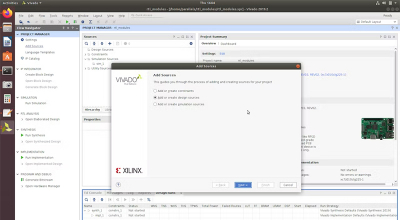

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题

本文介绍在使用源文件加密时的一些基本概念以及一些常见的问题

今天就通过一个简单的工程来看下如何在vivado软件中查看时序报告

在设计过程中,各个阶段的生成的文件都是.dcp,Vivado使用的是通用的模型贯穿在设计。

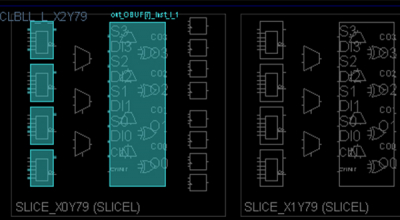

本文介绍RTL分析、综合、实现的具体含义和区别

为什么要修改IP核内的源码,说如何之前,先说为什么。

最近刚好新项目外场联调需要配置新电脑,因此正好可以用上intel的十三香了

Vitis是Xilinx SDK的继承开发工具,从Vivado 2019.2版本开始启用

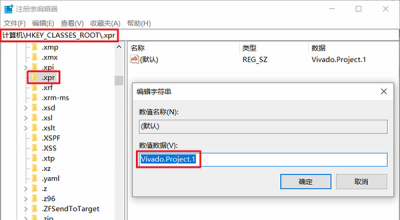

之前安装的Vivado 2018.3,最近装了Vivado 2020.2,然后就没法双击打开xpr工程文件了