HyperAccel 借助 AMD 加速卡与 FPGA 打造全新 AI 推理服务器

judy 在 周四, 06/13/2024 - 17:35 提交

HyperAccel 已经打造出一个快速、高效且低成本的推理系统,加速了基于转换器的大型语言模型( LLM )的推理

HyperAccel 已经打造出一个快速、高效且低成本的推理系统,加速了基于转换器的大型语言模型( LLM )的推理

在 Windows 操作系统中,环境变量可从项目导航 GUI 中进行设置或复原。

AMD Vivado™ Design Suite 2024.1 可立即下载。最新版本支持全新 AMD MicroBlaze™ V 软核处理器

为加快产品原型设计过程,安富利在Ultra96-V2开发板的基础上,设计了基于安森美Sensor的双目摄像头扩展子卡,推出全新的解决方案

相比GPU,FPGA性价比如何?在LLM领域,FPGA会有一席之地吗?

在使用Synplify综合时,此工具会自动优化我的设计。

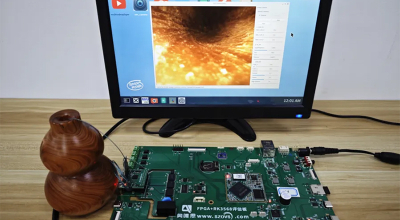

奥唯思第1代采用FPGA的加速的医疗内窥镜原型样机,发布!

下面我们先简单看下RISC-V的发展,然后再分析一下这些FPGA厂商为什么选择RISC-V。

近年来,深度学习框架的快速发展使得人工智能应用领域取得了巨大的进步。其中,Caffe框架以其简单易用、高效快速的特点受到了广泛关注和应用。

逻辑锁定功能可以将FPGA中的代码模块在固定区域实现,优化时序性能,提升设计可靠性。