Vivado ML 版中动态函数交换的技术进步

judy 在 周五, 07/30/2021 - 10:18 提交

本文描述如何使用 Dynamic Function eXchange 灵活高效地使用硬件资源来动态更新已部署的系统。包括对技术历史的回顾。

本文描述如何使用 Dynamic Function eXchange 灵活高效地使用硬件资源来动态更新已部署的系统。包括对技术历史的回顾。

本视频介绍深圳市艾为智能有限公司的CMS及BSD方案

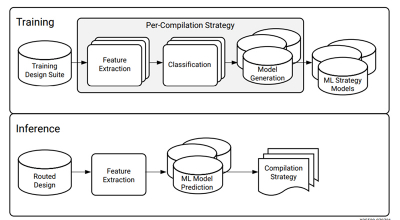

本白皮书描述智能设计如何使用机器学习和基于规则的系统来模拟时序收敛专家并提高生产力。

今天对于越来越多的人来说,人工智能(AI)已经不再是一个很“玄”的概念,而是实实在在走到了我们的身边。其中视觉AI应用就是离我们最近的一个。不论是无处不在的“刷脸”身份认证,还是工业生产线上的机器视觉检测,或者是汽车的自动驾驶,视觉AI应用正在快速渗透到我们生活中的方方面面。

Versal™Premium 系列符合 PCIe® 规范修订版 5.0,并且通过每条通道每秒 32 千兆次传输的速度支持全部链路速率。该视频演示了 Versal Premium ACAP 中面向 PCIe 的两个可用子系统,这在下一代网络和云基础架构中至关重要。

Kria系列是专门针对边缘部署而精心设计的SOM产品组合,从入门套件到生产SOM,无所不包,可简化系统开发,助力加速产品上市进程。KV260 入门套件是一款功能齐全的评估套件,能够利用预构建的加速应用来快速开发独特的解决方案,以在 K26 SOM 上进行生产部署。

赛灵思 Vitis AI 是一款功能强大的机器学习开发平台,用于在赛灵思自适应计算平台上实现 AI 推断加速。最新发布的 Vitis AI 1.4 版本为用户提供了完整的解决方案堆栈,首次实现了对最新 7nm Versal ACAP 平台和16nm Kria™ SOM的支持。

赛灵思开发者计划是一项面向全球开发者朋友推出的专项服务计划,打造了涵盖课程学习、项目开发、交流分享三大板块的自循环开发者生态体系,同时开放了多项权益(免费课程培训、硬件借用、专属活动邀请、新工具试用、自适应挑战赛激励和月度项目推荐等)

本视频介绍雪湖科技基于赛灵思FPGA推出的LiDAREYE解决方案。

为处理海量数据、复杂算法、超低延时的应用提供数字化加速驱动力是赛灵思一直的目标。为此,赛灵思研发 Bootgen 工具支持将二进制文件缝合在一起并生成器件启动镜像定义了多个属性和参数作为创建启动镜像时的输入。