智能化加速标准和协议的更新并推动验证IP(VIP)在芯片设计中的更广泛应用

judy 在 周五, 01/24/2025 - 15:40 提交

本文诠释了为什么在今天的电子行业中更加需要使用VIP在验证环境中来改进调试、覆盖收敛和提升质量,以加快项目交付和增加投资回报

本文诠释了为什么在今天的电子行业中更加需要使用VIP在验证环境中来改进调试、覆盖收敛和提升质量,以加快项目交付和增加投资回报

在技术飞速发展的今天,新兴的航空电子、关键基础设施和汽车应用正在重新定义人们对现场可编程门阵列(FPGA)的期望

FPGA 通常按照逻辑容量进行分类,这种方式固然简单,但未能充分体现现代 FPGA 作为可更改的片上系统所能提供的丰富功能和资源。

本期主要介绍智多晶DDR Controller的常见应用领域、内部结构、各模块功能、配置界面、配置参数等内容。

本应用手册可用于指导将 TPS65219 电源管理集成电路 (PMIC) 集成到为 Xilinx® Zynq® UltraScale+® 系列 MPSoC 供电的系统中

图像腐蚀算法是形态学图像处理中的一种基本操作,类似于“领域被蚕食”的过程。这种操作可以将图像中的前景色区域进行缩减细化

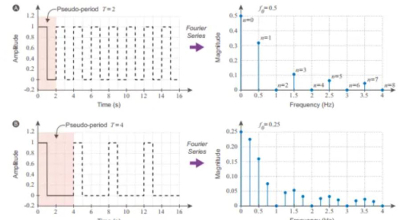

周期波形的傅里叶级数包含基频的谐波。我们可以使用如图4.14右侧所示的频率幅值图来绘制时域波形的谐波

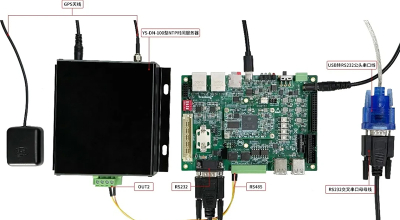

今天分享一个基于复旦微FMQL20S400M四核ARM Cortex-A7(PS端)+FPGA可编程逻辑资源(PL端)异构多核SoC处理器的B码对时案例,开发环境如下

AMD Alveo V80加速器卡基于7nm Versal™自适应SoC架构,采用AMD Versal高带宽内存(HBM)器件,提供速度高达820GB/s的4x200G网络

本文总结了业界用于高性能 USB 3 设备的一些典型解决方案,并介绍了一种新的架构,这种架构既能节省功耗和面积,又能提高灵活性和易用性