恭喜戴姆勒!梅赛德斯-奔驰 CLA 全球首发使用 MBUX 车内辅助功能

judy 在 周五, 01/11/2019 - 10:24 提交

2019 CES 展上,戴姆勒公司展出了其全球首发使用 MBUX 车内辅助的奔驰CLA 车型。该系统利用人工智能(AI)识别车辆乘客的自然动作及背景,让车辆可以预测驾驶员和乘客的需求,并且无需使用任何按钮即可满足此类需求。

2019 CES 展上,戴姆勒公司展出了其全球首发使用 MBUX 车内辅助的奔驰CLA 车型。该系统利用人工智能(AI)识别车辆乘客的自然动作及背景,让车辆可以预测驾驶员和乘客的需求,并且无需使用任何按钮即可满足此类需求。

MINIEYE在 2019 年 CES 上正式对外宣布,与赛灵思公司就携手开发一站式ADAS感知解决方案 (Turnkey Sensing Solution)达成技术合作。双方将通过把 MINIEYE 的 IP 运行在赛灵思 Zynq®-7000 SoC 和 Zynq® UltraScale+™ 车级 MPSoC 平台上的形式,共同满足全球 L0-L3 级自动驾驶需求。

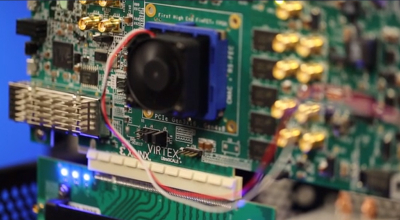

本视频重点介绍首款构建在可编程逻辑器件中的 Gen3 x16 PCI Express 解决方案,该方案通过了 4/2016 PCI SIG 合规性测试。该演示展示了 PCIe 在 Virtex UltraScale+ FPGA 电路板上启动和运行,并连接至 Intel Skylake 处理器

计算存储的 Nuts 与 Bolts

此演示展示了一个密集的 AMD EPYC 服务器,支持多达八个 Alveo U200 / U250 加速卡,可为计算密集型应用提供最高的自适应计算密度。该系统还配备了一款超微主板。该系统可用来加速基因组学、视频、大数据以及金融等领域的应用。

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

一、Black Box调用HDL代码

1、简介

System Generator提供了一个特性:可以通过black box这个block将其它HDL文件以黑盒的形式封装到System Generator设计中,在仿真时使用Simulink+Vivado Simulator(或ModelSim)协同仿真的方法,在Simulink环境中完成设计的仿真测试。

具体介绍大家可以查阅相关资料。

2、本部分设计使用到的block

Xilinx block

其它block

该系列文章介绍MIPI系列规范。本篇为第一篇,主要介绍MIPI Alliance及其推出的一系列规范,以及相关的一些应用,以便对MIPI有一个全面的了解。后续会针对每一个部分进行详细介绍。

1、MIPI Overview

DDS直接数字式频率合成器(Direct Digital Synthesizer)。本文实现一个具有可以频率可调、相位可调的正余弦、方波、三角波的DDS。

使用 Vivado 设计套件中的各种设计分析特性。

内核重置应该保持断言状态,直到相关时钟稳定为止。在从重置中取出以太网 IP 核之前,它必须具有稳定的频率而且没有故障。 这适用于 SerDes 时钟和 IP 核时钟。 如果在一个时钟中检测到后续不稳定性,就必须重置 100G 以太网 IP 核。