Xilinx A7 芯片内部结构分析(1)—— CLB

judy 在 周三, 12/05/2018 - 09:23 提交

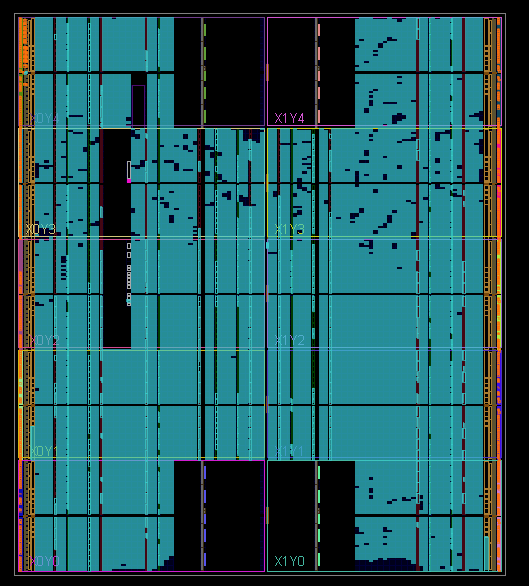

一直以来,觉得自己关于FPGA方面,摸不到“低”——对底层架构认识不清,够不着“高”——没真正独立做过NB的应用,如高速、复杂协议或算法、神经网络加速等高大上的应用,所以能力和认识水平都处于中间水平。这段时间做时序优化,感觉心有余而力不足了,可能要触及手动布局布线了,打开Device布局图才开始有兴趣探究一些底层结构的东西。

看吧,资源已经用了80%的A7 200芯片

可能翻开任何一本有关FPGA的书籍,上来就会介绍FPGA的历史,原理,内部结构什么的,大部分人看着都极其枯燥,常常要么直接略过,要么就看一遍,久了也就忘记了(部分靠翻译文档的书作者该好好反思)。我硬着头皮去弥补之前缺失的一些基础知识,结合Xilinx A7 芯片,总结一下自己的收获。