【视频】软件与 IP 产品执行副总裁 Salil Raje 与您分享 AI 加速

judy 在 周五, 10/26/2018 - 15:31 提交

聆听软件与 IP 产品执行副总裁 Salil Raje 与您分享最新的 Xilinx 机器学习战略

聆听软件与 IP 产品执行副总裁 Salil Raje 与您分享最新的 Xilinx 机器学习战略

作者:没落骑士

一、前言

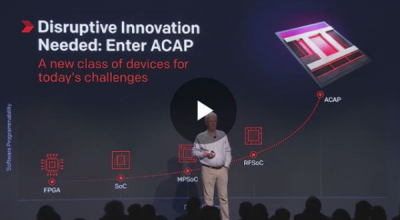

Versal 是我们的下一代架构,请跟随硬件和系统产品开发执行副总裁 Liam Madden ,了解更多有关 Versal 的信息。

10月16日,赛灵思开发者大会(XDF)北京站在北京国际饭店举办。本次大会围绕“学习,交流,分享”的主题,展示了当下众多热门应用、创意以及设计案例,亚马逊、华为、浪潮等数十家国内外厂商参展,科通集团(港股代码:400HK)作为重要合作伙伴出席开发者大会并在现场设置了展位,展示了科通及其客户在赛灵思FPGA产品上的应用与发展。

AXI-DMA的linux驱动

一、搭建硬件环境

vivado版本2017.4,芯片为7010,不过不管什么版本和芯片大致步骤是一样的

一. 概述

这里以7系列的FPGA为例,先从整体上去了解一下FPGA内部可编程逻辑资源的结构。了解FPGA器件的内部资源与结构有利于我们优化设计与评估设计资源。

2018年10月16日,全球FPGA芯片巨头Xilinx在北京举行Xilinx开发者大会,Xilinx全球总裁兼CEO Victor Peng发表了“面向灵活应变,万物智能世界的平台”的主题演讲。作为Xilinx在国内智能汽车电子领域的Certificated Member,深圳市自行科技有限公司(简称:自行科技)受邀参加,公司联合创始人兼CEO关艳峰博士与CTO谌璟博士出席。

串行外设接口(SPI)是微控制器和外围IC(如传感器、ADC、DAC、移位寄存器、SRAM等)之间使用最广泛的接口之一。本文先简要说明SPI接口,然后介绍ADI公司支持SPI的模拟开关与多路转换器,以及它们如何帮助减少系统电路板设计中的数字GPIO数量。

作者:OpenSLee,来源:FPGA开源工作室

1背景知识